- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377798 > LXT351QE (INTEL CORP) PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT351QE |

| 廠商: | INTEL CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 27/46頁 |

| 文件大小: | 1132K |

| 代理商: | LXT351QE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

T1/E1 Short Haul Transceiver with Crystal-less Jitter Attenuation

—

LXT351

Datasheet

27

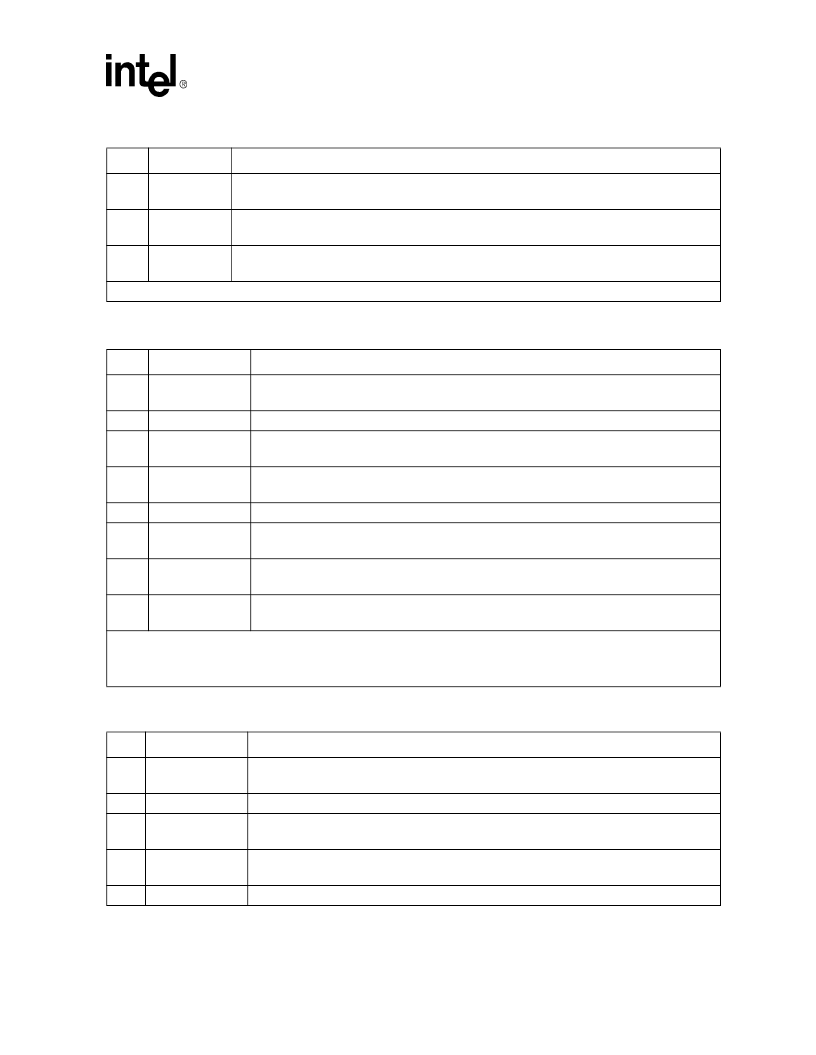

5

CDFMO

1 = Clear/Mask Driver Failure Monitor Open interrupt.

0 = Enable Driver Failure Monitor Open interrupt.

6

CESO

1 = Clear/Mask Elastic Store Overflow interrupt.

0 = Enable Elastic Store Overflow interrupt.

7

CESU

1 = Clear/Mask Elastic Store Underflow interrupt.

0 = Enable Elastic Store Underflow interrupt.

Table 12. Transition Status Register

Read Only, Address (A7-A0) = x010100x

Bit

Name

Function

0

TLOS

1 = Loss of Signal (LOS) has changed since last clear LOS interrupt occurred.

0 = No change in status.

1

-

Reserved. Ignore.

2

TAIS

1 = AIS has changed since last clear AIS interrupt occurred.

0 = No change in status.

3

TQRSS

1 = QRSS has changed since last clear QRSS interrupt occurred

1

.

0 = No change in status.

4

-

Reserved. Ignore.

5

TDFMO

1 = DFMO has changed since last clear DFMS interrupt occurred.

0 = No change in status.

6

ESOVR

1 = ES overflow status sticky bit

2

.

0 = No change in status.

7

ESUNF

1 = ES underflow status sticky bit

.

0 = No change in status.

1. A QRSS transition indicates receive QRSS pattern sync or loss. A simple error in QRSS pattern is not reported as a

transition.

2. Tripping the overflow or underflow indicator in the ES sets the ESOVR/ESUNF status bit(s). Reading the Transition Status

Register clears these bits. Setting CESO and CESU in the Interrupt Clear Register masks these interrupts.

Table 13. Performance Status Register

Read Only, Address (A7-A0) = x010101x

Bit

Name

Function

0

LOS

1 = Loss of Signal occurred.

0 = Loss of Signal did not occur.

1

-

Reserved. Ignore.

2

AIS

1 = Alarm Indicator Signal detected.

0 = Alarm Indicator Signal not detected.

3

QRSS

1 = Quasi-Random Signal Source pattern detected.

0 = Quasi-Random Signal Source pattern not detected.

4

-

Reserved. Ignore.

Table 11. Interrupt Clear Register

Read/Write, Address (A7-A0) = x010011x

Bit

Name

Function

1

1. Leaving a 1 of in any of these bits masks the associated interrupt.

相關PDF資料 |

PDF描述 |

|---|---|

| LXT361QE | Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT360 | Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT361 | Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT360QE | CONNECTOR ACCESSORY |

| LXT381BE | Octal E1 Line Interface Unit |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LXT360 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

| LXT360LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

| LXT360PE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|LDCC|28PIN|PLASTIC |

| LXT360QE | 制造商:Intel 功能描述: 制造商:LEVEL ONE 功能描述: |

| LXT361 | 制造商:LVL1 制造商全稱:LVL1 功能描述:Integrated T1/E1 LH/SH Transceivers for DS1/DSX-1/CSU or NTU/ISDN PRI Applications |

發(fā)布緊急采購,3分鐘左右您將得到回復。