- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M13S32321A (Elite Semiconductor Memory Technology Inc.) 256K x 32 Bit x 4 Banks Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號: | M13S32321A |

| 廠商: | Elite Semiconductor Memory Technology Inc. |

| 英文描述: | 256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| 中文描述: | 256K × 32位× 4個銀行雙倍數(shù)據(jù)速率SDRAM |

| 文件頁數(shù): | 19/49頁 |

| 文件大小: | 769K |

| 代理商: | M13S32321A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁

ES MT

M13S32321A

Elite Semiconductor Memory Technology Inc.

Publication Date : Sep. 2006

Revision : 1.0 19/49

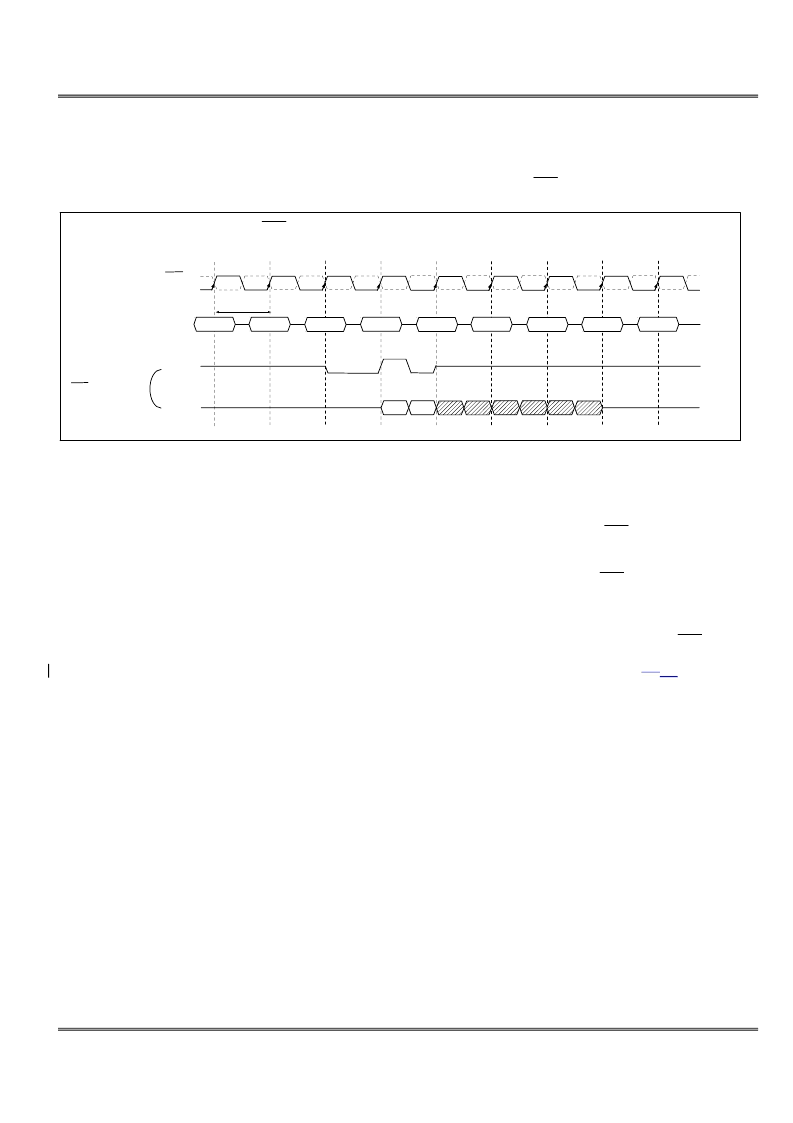

Read Interrupted by a Precharge

A Burst Read operation can be interrupted by precharge of the same bank. The minimum 1 clock is required for the read to

precharge intervals. A precharge command to output disable latency is equivalent to the CAS latency.

<Burst Length = 8, CAS Latency = 3>

When a burst Read command is issued to a DDR SDRAM, a Precharge command may be issued to the same bank before the

Read burst is complete. The following functionality determines when a Precharge command may be given during a Read burst and

when a new Bank Activate command may be issued to the same bank.

1. For the earliest possible Precharge command without interrupting a Read burst, the Precharge command may be given on the

rising clock edge which is CL clock cycles before the end of the Read burst where CL is the CAS Latency. A new Bank

Activate command may be issued to the same bank after t

RP

(RAS precharge time).

2. When a Precharge command interrupts a Read burst operation, the Precharge command may be given on the rising clock edge

which is CL clock cycles before the last data from the interrupted Read burst where CL is the CAS Latency. Once the last

data word has been output, the output buffers are tristated. A new Bank Activate command may be issued to the same bank

after t

RP

.

3. For a Read with autoprecharge command, a new Bank Activate command may be issued to the same bank after t

RP

where t

RP

begins on the rising clock edge which is CL clock cycles before the end of the Read burst where CL is the CAS Latency.

During Read with autoprecharge, the initiation of the internal precharge occurs at the same time as the earliest possible

external Precharge command would initiate a precharge operation without interrupting the Read burst

ad as

described in 1

above.

4. For all cases above, t

RP

is an analog delay that needs to be converted into clock cycles. The number of clock cycles between a

Precharge command and a new Bank Activate command to the same bank equals t

RP

/ t

CK

(where t

CK

is the clock cycle time)

with the result rounded up to the nearest integer number of clock cycles.

In all cases, a Precharge operation cannot be initiated unless t

RAS

(min) [minimum Bank Activate to Precharge time] has been

satisfied. This includes Read with autoprecharge commands where t

RAS

(min) must still be satisfied such that a Read with

autoprecharge command has the same timing as a Read command followed by the earliest possible Precharge command which

does not interrupt the burst.

C A S L at e n c y= 3

0

1

2

3

4

5

6

7

8

CO MM AN D

DQS

DQ 's

READ

NOP

NOP

NOP

NOP

NOP

NOP

Dout 0

Precharge

Dout 1

1t

C K

NOP

Dout 2 Dout 3 Dout 4 Dout 5

In t er r u p t ed b y p r e c h a r g e

Dout 6 Dout 7

C L K

C L K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M13S64164A-6BG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-5BG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-5TG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6TG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M13S32321A_08 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S32321A-5L | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S32321A-6L | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S5121632A | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:8M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S5121632A-5TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:8M x 16 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。