- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377801 > M13S32321A (Elite Semiconductor Memory Technology Inc.) 256K x 32 Bit x 4 Banks Double Data Rate SDRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M13S32321A |

| 廠商: | Elite Semiconductor Memory Technology Inc. |

| 英文描述: | 256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| 中文描述: | 256K × 32位× 4個(gè)銀行雙倍數(shù)據(jù)速率SDRAM |

| 文件頁(yè)數(shù): | 4/49頁(yè) |

| 文件大小: | 769K |

| 代理商: | M13S32321A |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)

ES MT

M13S32321A

Elite Semiconductor Memory Technology Inc.

Publication Date : Sep. 2006

Revision : 1.0 4/49

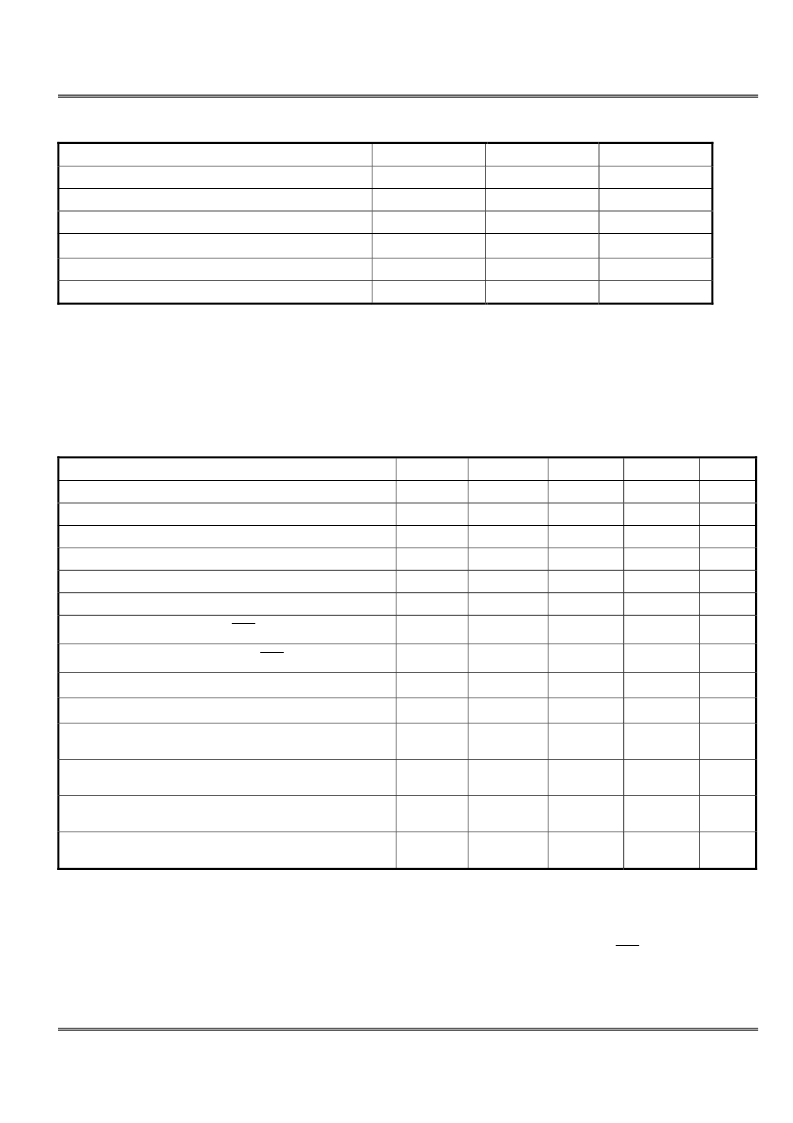

Absolute Maximum Rating

Parameter

Symbol

Value

Unit

Voltage on any pin relative to V

SS

V

IN

, V

OUT

-0.5 ~ 3.6

V

Voltage on V

DD

supply relative to V

SS

V

DD

, V

DDQ

-1.0 ~ 3.6

V

Voltage on V

DDQ

supply relative to V

SS

V

DDQ

-0.5 ~ 3.6

V

Storage temperature

T

STG

-55 ~ +150

C

°

Power dissipation

P

D

1.0

W

Short circuit current

I

OS

50

mA

Note : Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommend operation condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC Operation Condition & Specifications

DC Operation Condition

Recommended operating conditions (Voltage reference to V

SS

= 0V, T

A

= 0 to 70° )

Parameter

Symbol

Min

Max

Unit

Note

Supply voltage

V

DD

2.375

2.625

V

I/O Supply voltage

V

DDQ

2.375

2.625

V

I/O Reference voltage

V

REF

0.49*V

DDQ

0.51*V

DDQ

V

1

I/O Termination voltage (system)

V

TT

V

REF

- 0.04

V

REF

+ 0.04

V

2

Input logic high voltage

V

IH

(DC)

V

REF

+ 0.15

V

DDQ

+ 0.3

V

Input logic low voltage

V

IL

(DC)

-0.3

V

REF

- 0.15

V

Input Voltage Level, CLK and CLK inputs

V

IN

(DC)

-0.3

V

DDQ

+ 0.3

V

Input Differential Voltage, CLK and CLK inputs

V

ID

(DC)

0.36

V

DDQ

+ 0.6

V

Input leakage current

I

I

-2

2

μ

A

3

Output leakage current

I

OZ

-5

5

μ

A

Output High Current (Normal strength driver)

(V

OUT

=V

DDQ

-0.373V, min V

REF

, min V

TT

)

I

OH

-16.8

mA

Output Low Current (Normal strength driver)

(V

OUT

= 0.373V)

I

OL

+16.8

mA

Output High Current (Weak strength driver)

(V

OUT

=V

DDQ

-0.763V, min V

REF

, min V

TT

)

I

OH

-9

mA

Output Low Current (Weak strength driver)

(V

OUT

= 0.763V)

I

OL

+9

mA

Notes 1. V

REF

is expected to be equal to 0.5* V

DDQ

of the transmitting device, and to track variations in the DC level of the same.

Peak-to-peak noise on V

REF

may not exceed 2% of the DC value.

3.

V

TT

is not applied directly to the device. V

TT

is system supply for signal termination resistors, is expected to be set

equal to V

REF

, and must track variations in the DC level of V

REF

.

3.

V

ID

is the magnitude of the difference between the input level on CLK and the input level on CLK .

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M13S64164A-6BG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-5BG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-5TG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S64164A-6TG | 1M x 16 Bit x 4 Banks Double Data Rate SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M13S32321A_08 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S32321A-5L | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S32321A-6L | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:256K x 32 Bit x 4 Banks Double Data Rate SDRAM |

| M13S5121632A | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:8M x 16 Bit x 4 Banks Double Data Rate SDRAM |

| M13S5121632A-5TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:8M x 16 Bit x 4 Banks Double Data Rate SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。