- 您現在的位置:買賣IC網 > PDF目錄359068 > M48Z19-100PC1 (意法半導體) CMOS 8K x 8 ZEROPOWER SRAM PDF資料下載

參數資料

| 型號: | M48Z19-100PC1 |

| 廠商: | 意法半導體 |

| 英文描述: | CMOS 8K x 8 ZEROPOWER SRAM |

| 中文描述: | 的CMOS 8K的× 8 ZEROPOWER的SRAM |

| 文件頁數: | 3/13頁 |

| 文件大小: | 122K |

| 代理商: | M48Z19-100PC1 |

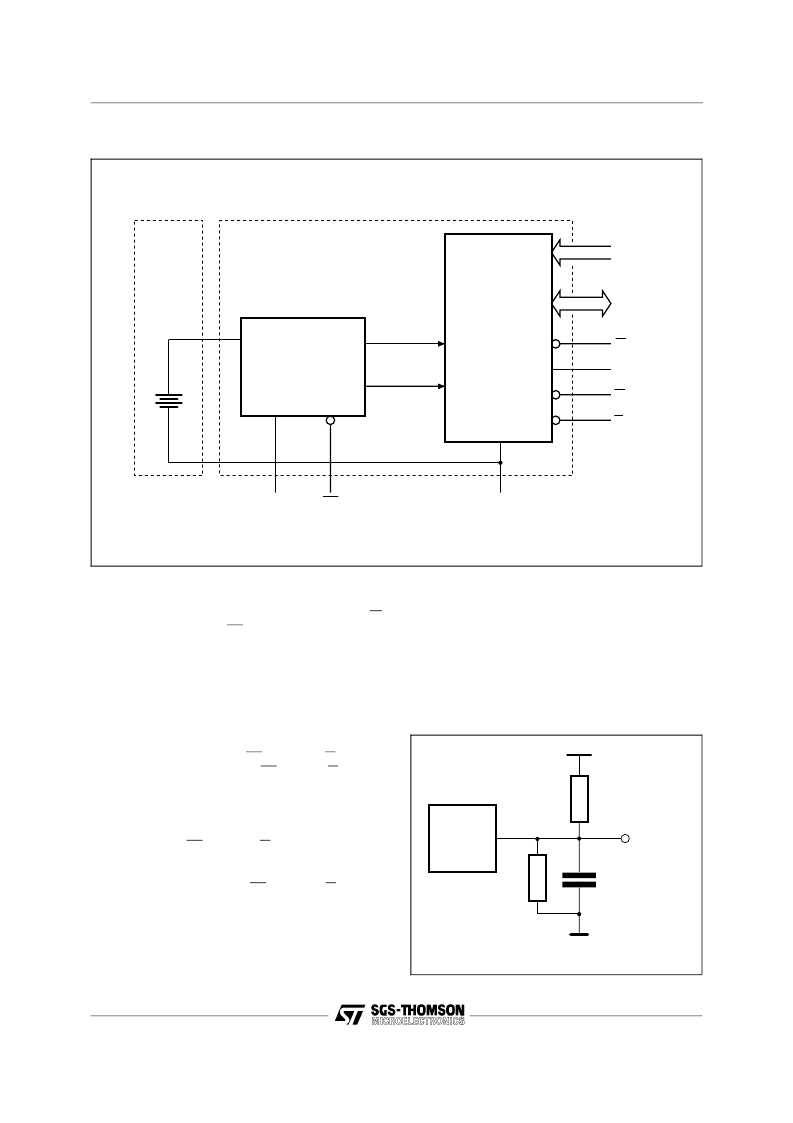

AI01398

5V

OUT

CL = 100pF or 30pF

CL includes JIG capacitance

1.8k

DEVICE

UNDER

TEST

1k

Figure 4. AC Testing Load Circuit

Input Rise and Fall Times

Input Pulse Voltages

Input and Output Timing Ref. Voltages

≤

5ns

0 to 3V

1.5V

AC MEASUREMENT CONDITIONS

Note that Output Hi-Z is defined as the point where data

is no longer driven.

AI01397

LITHIUM

CELL

VPFD

VCC

VSS

VOLTAGE SENSE

AND

SWITCHING

CIRCUITRY

8K x 8

SRAM ARRAY

A0-A12

DQ0-DQ7

E1

W

G

POWER

E2

INT

Figure 3. Block Diagram

READ MODE

The M48Z09,19 is in the Read Mode whenever W

(Write Enable) is high, E1 (Chip Enable 1) is low,

and E2 (Chip Enable 2) is high. The device archi-

tecture allows ripple- through access of data from

eight of 65,536 locations in the static storage array.

Thus, the unique address specified by the 13 Ad-

dress Inputs defines which one of the 8,192 bytes

of data is to be accessed. Valid data will be avail-

able at the Data I/O pins within t

AVQV

(Address

Access Time) after the last address input signal is

stable, providing that the E1, E2, and G access

times are also satisfied. If the E1, E2 and G access

times are not met, valid data will be available after

the latter of the Chip Enable Access Times (t

E1LQV

or t

E2HQV

) or Output Enable Access Time (t

GLQV

).

The state of the eight three-state Data I/O signals

is controlled by E1, E2 and G. If the outputs are

activated before t

AVQV

, the data lines will be driven

to an indeterminate state until t

AVQV

. If the Address

Inputs are changed while E1, E2 and G remain

active, output data will remain valid for t

AXQX

(Out-

put Data Hold Time) but will go indeterminate until

the next Address Access.

3/13

M48Z09, M48Z19

相關PDF資料 |

PDF描述 |

|---|---|

| M48Z2M1-70PL1 | 16 Mb 2Mb x 8 ZEROPOWER SRAM |

| M48Z2M1Y-70PL1 | 16 Mb 2Mb x 8 ZEROPOWER SRAM |

| M48Z2M1-70PL9 | 16 Mb 2Mb x 8 ZEROPOWER SRAM |

| M48Z2M1Y-70PL9 | 16 Mb 2Mb x 8 ZEROPOWER SRAM |

| M48Z2M1 | 122 x 32 pixel format, Compact LCD size |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M48Z19PC | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:CMOS 8K x 8 ZEROPOWER SRAM |

| M48Z256-85PL1 | 制造商:STMicroelectronics 功能描述:512KX8 ZP 5% 85NS - Bulk |

| M48Z256Y-120PL1 | 制造商:STMicroelectronics 功能描述:256KX8 ZP 10% 120N - Bulk |

| M48Z256Y-85PL1 | 制造商:STMicroelectronics 功能描述:256KX8 ZP 10% 85NS - Bulk |

| M48Z2M1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Mb 2Mb x 8 ZEROPOWER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。