- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180472 > MACH131SP-15YC (LATTICE SEMICONDUCTOR CORP) High-Performance EE CMOS Programmable Logic PDF資料下載

參數(shù)資料

| 型號: | MACH131SP-15YC |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | High-Performance EE CMOS Programmable Logic |

| 中文描述: | EE PLD, 15 ns, PQFP100 |

| 封裝: | PLASTIC, QFP-100 |

| 文件頁數(shù): | 22/47頁 |

| 文件大?。?/td> | 1200K |

| 代理商: | MACH131SP-15YC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

MACH 1 & 2 Families

29

MACH221 and MACH221SP

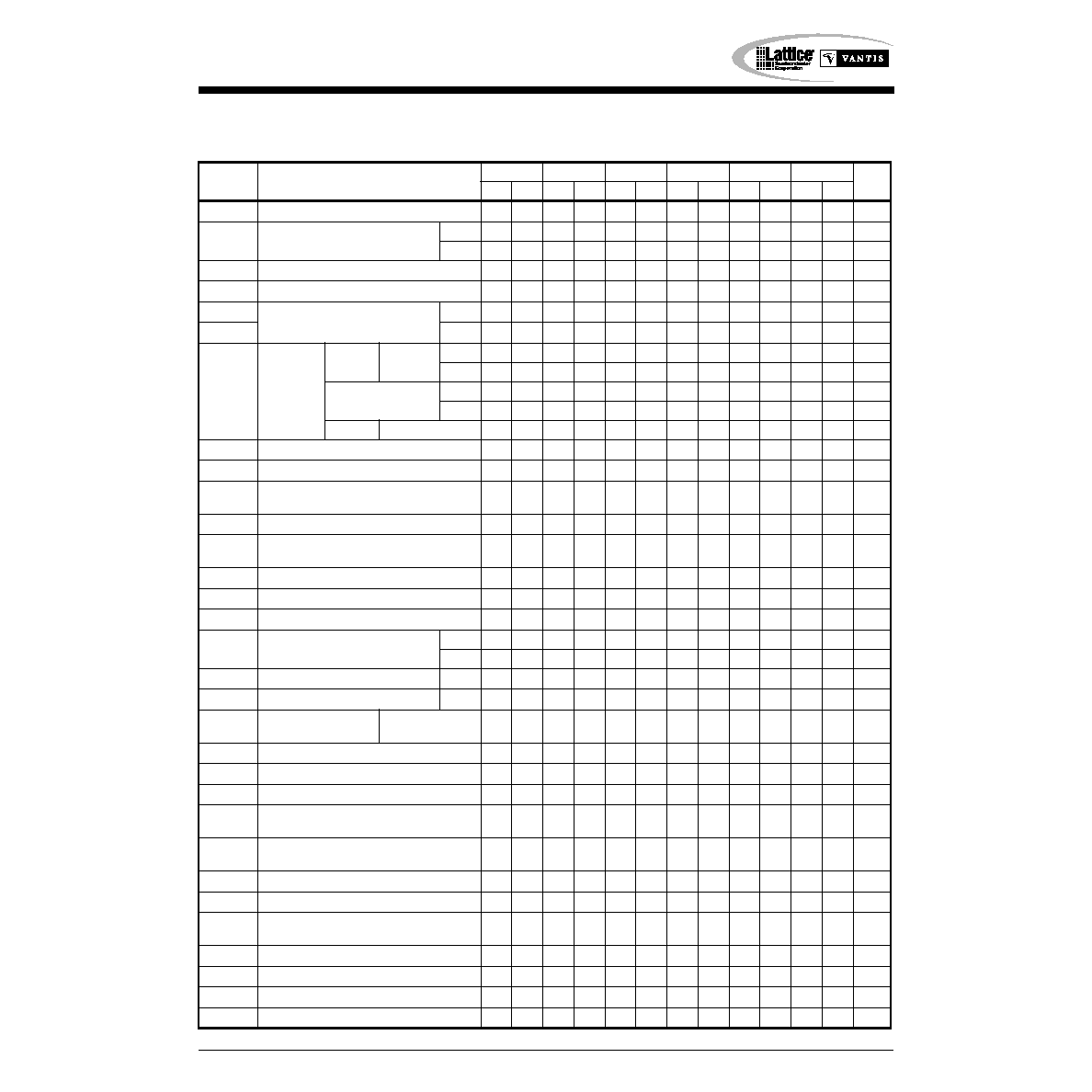

SWITCHING CHARACTERISTICS OVER OPERATING RANGES1

Parameter

Symbol

Parameter Description

-7

-10

-12

-14

-15

-18

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

tPD

Input, I/O, or Feedback to Combinatorial Output

7.5

10

12

14

15

18

ns

ts

Setup Time from Input, I/O, or Feedback to

Clock

D-type

5.5

6.5

7

8.5

10

12

ns

T-type

6.5

7.5

8

10

11

13.5

ns

tH

Register Data Hold Time

000000

ns

tCO

Clock to Output

5

6

8

10

12

ns

tWL

Clock Width

LOW

35666

7.5

ns

tWH

HIGH

35666

7.5

ns

fMAX

Maximum

Frequency

External

Feedback

1/(tS + tCO)

D-type

95

80

66.7

54

50

42

MHz

T-type

87

74

62.5

50

47.6

39

MHz

Internal Feedback (fCNT)

D-type

133

100

83.3

69

66.6

55.6

MHz

T-type

125

91

76.9

62.5

51.3

MHz

No Feedback 1/(tWL + tWH)

167

100

83.3

66.7

MHz

tSL

Setup Time from Input, I/O, or Feedback to Gate

5.5

6.5

7

8.5

10

12

ns

tHL

Latch Data Hold Time

000000

ns

tGO

Gate to Output

7

(note 2)

10

11

13.5

ns

tGWL

Gate Width LOW

35666

7.5

ns

tPDL

Input, I/O, or Feedback to Output Through Transparent

Input or Output Latch

9.5

12

14

17

20.5

ns

tSIR

Input Register Setup Time

22222

2.5

ns

tHIR

Input Register Hold Time

2

2.5

3.5

ns

tICO

Input Register Clock to Combinatorial Output

11

13

15

18

22

ns

tICS

Input Register Clock to Output Register Setup

D-type

9

10

12

14.5

15

18

ns

T-type

10

11

13

16

19.5

ns

tWICL

Input Register

LOW

35666

7.5

ns

tWICH

Clock Width

HIGH

35666

7.5

ns

fMAXIR

Maximum Input Register

Frequency

1/(tWICL + tWICH)

167

100

83.3

66.7

MHz

tSIL

Input Latch Setup Time

22222

2.5

ns

tHIL

Input Latch Hold Time

2

2.5

3.5

ns

tIGO

Input Latch Gate to Combinatorial Output

12

14

17

20

24

ns

tIGOL

Input Latch Gate to Output Through Transparent Output

Latch

14

16

19

22

26.5

ns

tSLL

Setup Time from Input, I/O, or Feedback Through

Transparent Input Latch to Output Latch Gate

7.5

8.5

9

11

12

14.5

ns

tIGS

Input Latch Gate to Output Latch Setup

10

11

13

16

19.5

ns

tWIGL

Input Latch Gate Width LOW

35666

7.5

ns

tPDLL

Input, I/O, or Feedback to Output Through Transparent

Input and Output Latches

11.5

14

16

19

23

ns

tAR

Asynchronous Reset to Registered or Latched Output

9.5

15

16

19.5

20

24

ns

tARW

Asynchronous Reset Width (Note 3)

5

10

12

14.5

15

18

ns

tARR

Asynchronous Reset Recovery Time (Note 3)

5

8

10

12

ns

tAP

Asynchronous Preset to Registered or Latched Output

9.5

15

16

19.5

20

24

ns

相關PDF資料 |

PDF描述 |

|---|---|

| MACH131SP-5YC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-7YC | High-Performance EE CMOS Programmable Logic |

| MACH1 | High-Performance EE CMOS Programmable Logic |

| MACH210A-10JC | High-Density EE CMOS Programmable Logic |

| MACH210A-10VC | High-Density EE CMOS Programmable Logic |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MACH131SP-18YI | 功能描述:CPLD - 復雜可編程邏輯器件 HI PERF EE CMOS PLD RoHS:否 制造商:Lattice 系列: 存儲類型:EEPROM 大電池數(shù)量:128 最大工作頻率:333 MHz 延遲時間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| MACH131SP-5VC | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH131SP-5YC | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH131SP-7VC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MACH131SP-7YC | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

發(fā)布緊急采購,3分鐘左右您將得到回復。