- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377930 > MB90F897S (Fujitsu Limited) 10-Bit Buffers/Drivers With 3-State Outputs 28-LCCC -55 to 125 PDF資料下載

參數(shù)資料

| 型號: | MB90F897S |

| 廠商: | Fujitsu Limited |

| 英文描述: | 10-Bit Buffers/Drivers With 3-State Outputs 28-LCCC -55 to 125 |

| 中文描述: | 16位微控制器專有 |

| 文件頁數(shù): | 44/78頁 |

| 文件大小: | 746K |

| 代理商: | MB90F897S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

MB90895 Series

44

9.

DTP/External Interrupt and CAN Wakeup Outline

DTP/external interrupt transfers an interrupt request generated by an external peripheral device or a data trans-

mission request to CPU, generating external interrupt request and activating expanded intelligent I/O service.

Input RX of CAN controller is used as external interrupt input.

DTP/external interrupt and CAN wakeup function

An interrupt request input from external peripheral device to external input pins (INT7 to INT4) and RX pin, just

as interrupt request of peripheral device, generates an interrupt request. The interrupt request generates an

external interrupt and activates expanded intelligent I/O service (EI

2

OS).

If the expanded intelligent I/O service (EI

2

OS) has been disabled by interrupt control register (ICR: ISE=0),

external interrupt function is enabled and branches to interrupt processing.

If the EI

2

OS has been enabled, (ICR: ISE=1), DTP function is enabled and automatic data transmission is

performed by EI

2

OS. After performing specified number of data transmission processes, the process branches

to interrupt processing.

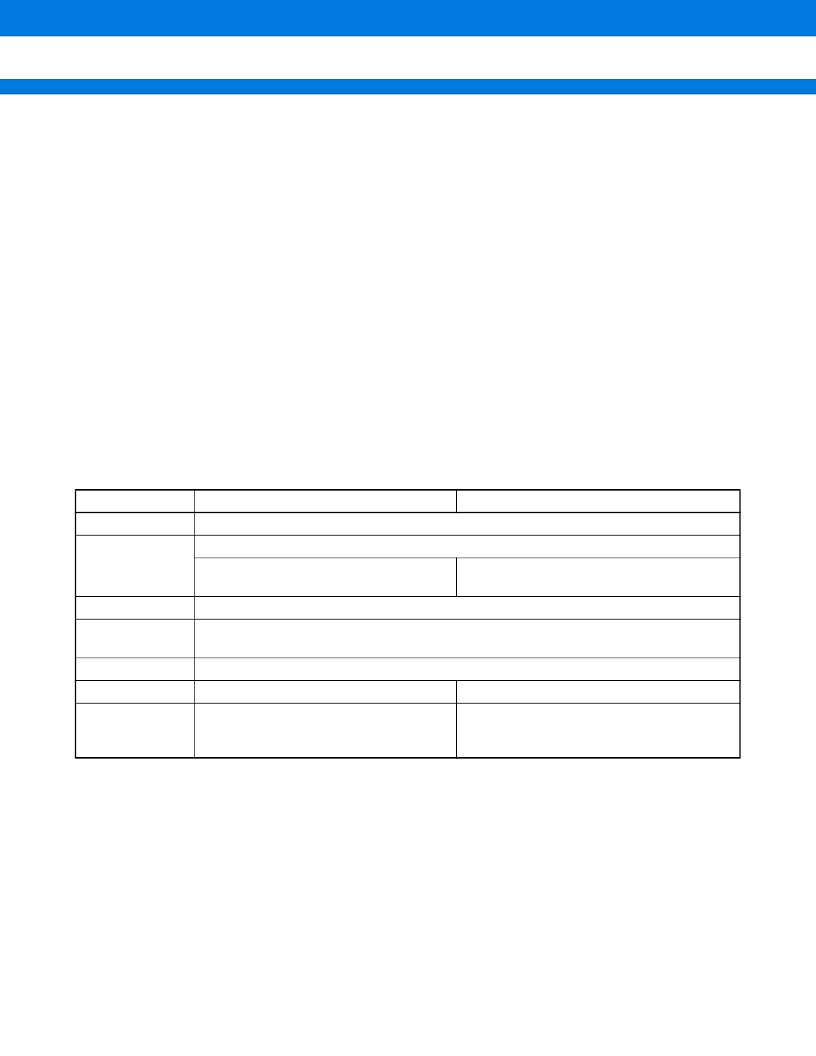

DTP/external interrupt and CAN wakeup outline

External interrupt

DTP function

Input pin

5 pins (RX, and INT4 to INT7)

Interrupt cause

Specify for each pin with detection level setting register (ELVR).

Input of “H” level/“L” level/rising edge/falling

edge.

Input of “H” level/ “L” level

Interrupt number

#15 (0F

H

) , #24 (18

H

) , #27 (1B

H

)

Interrupt control

Enabling or disabling output of interrupt request, using DTP/external interrupt permission

register (ENIR).

Interrupt flag

Retaining interrupt cause with DTP/external interrupt cause register (EIRR).

Process selection

Disable EI

2

OS (ICR: ISE=0)

Enable EI

2

OS (ICR: ISE=1)

Process

Branch to external interrupt process

After automatic data transmission by EI

2

OS for

specified number of times, branch to interrupt

process.

相關PDF資料 |

PDF描述 |

|---|---|

| MB90F897SPMT | 10-Bit Buffers/Drivers With 3-State Outputs 24-CDIP -55 to 125 |

| MB90M405 | Octal Edge-Triggered D-type Flip-Flops With Clear 20-CFP -55 to 125 |

| MB90M407 | Octal Edge-Triggered D-type Flip-Flops With Clear 20-LCCC -55 to 125 |

| MB90M408 | Octal Edge-Triggered D-type Flip-Flops With Clear 20-CDIP -55 to 125 |

| MB90MV405 | F2MC-16LX FAMILY 16-BIT MICROCONTROLLERS HARDWARE MANUAL ABSTRACTS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MB90F897SPMCR-GSE1 | 制造商:FUJITSU 功能描述: 制造商:FUJITSU 功能描述:MCU 16BIT 16LX 64K FLASH 48LQFP 制造商:FUJITSU 功能描述:MCU, 16BIT, 16LX, 64K FLASH, 48LQFP 制造商:FUJITSU 功能描述:IC, 16BIT MCU, F2MC-16LX, 16MHZ, LQFP-48, Controller Family/Series:F2MC-16LX, Core Size:16bit, No. of I/O's:36, Supply Voltage Min:3.5V, Supply Voltage Max:5.5V, Digital IC Case Style:LQFP, No. of Pins:48, Program Memory Size:64KB , RoHS Compliant: Yes 制造商:FUJITSU 功能描述:MCU, 16BIT, 16LX, 64K FLASH, 48LQFP, Controller Family/Series:F2MC-16LX, Core Si |

| MB90F947APFR-GS-SPE1 | 制造商:FUJITSU 功能描述: |

| MB90F962SPMCR-GE1 | 制造商:FUJITSU 功能描述:IC MCU 16BIT 16LX 48LQFP |

| MB90F962SPMCR-G-JNE1 | 制造商:FUJITSU 功能描述: |

| MB90V340A-102CR | 制造商:FUJITSU 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。