- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371046 > MC68B912B32 (Motorola, Inc.) 2.5V 100ppm/Degrees C, 50uA in SOT23-3 Series (Bandgap) Voltage Reference 3-SOT-23 -40 to 125 PDF資料下載

參數(shù)資料

| 型號: | MC68B912B32 |

| 廠商: | Motorola, Inc. |

| 英文描述: | 2.5V 100ppm/Degrees C, 50uA in SOT23-3 Series (Bandgap) Voltage Reference 3-SOT-23 -40 to 125 |

| 中文描述: | 16位微控制器 |

| 文件頁數(shù): | 55/128頁 |

| 文件大小: | 748K |

| 代理商: | MC68B912B32 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當(dāng)前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

MC68HC912B32

MC68HC912B32TS/D

MOTOROLA

55

9.5.2 Clock and Watchdog Control Logic

The COP watchdog system is enabled, with the CR[2:0] bits set for the shortest duration time-out. The

clock monitor is disabled. The RTIF flag is cleared and automatic hardware interrupts are masked. The

rate control bits are cleared, and must be initialized before the RTI system is used. The DLY control bit

is set to specify an oscillator start-up delay upon recovery from STOP mode.

9.5.3 Interrupts

PSEL is initialized in the HPRIO register with the value $F2, causing the external IRQ pin to have the

highest I-bit interrupt priority. The IRQ pin is configured for level-sensitive operation (for wired-OR sys-

tems). However, the interrupt mask bits in the CPU12 CCR are set to mask X and I related interrupt

requests.

9.5.4 Parallel I/O

If the MCU comes out of reset in an expanded mode, port A and port B are used for the multiplexed

address/data bus and port E pins are normally used to control the external bus (operation of port E pins

can be affected by the PEAR register). If the MCU comes out of reset in a single-chip mode, all ports

are configured as general-purpose high-impedance inputs. Port S, port T, port DLC, port P, and port AD

are all configured as general-purpose inputs.

9.5.5 Central Processing Unit

After reset, the CPU fetches a vector from the appropriate address, then begins executing instructions.

The stack pointer and other CPU registers are indeterminate immediately after reset. The CCR X and

I interrupt mask bits are set to mask any interrupt requests. The S bit is also set to inhibit the STOP

instruction.

9.5.6 Memory

After reset, the internal register block is located at $0000–$01FF, the register-following space is at

$0200–$03FF, and RAM is at $0800–$0BFF. EEPROM is located at $0D00–$0FFF. Flash EEPROM

is located at $8000–$FFFF in single-chip modes and at $0000–$7FFF (but disabled) in expanded

modes.

9.5.7 Other Resources

The timer, serial communications interface (SCI), serial peripheral interface (SPI), byte data link con-

troller (BDLC), pulse-width modulator (PWM), and analog-to-digital converter (ATD) are off after reset.

9.6 Register Stacking

Once enabled, an interrupt request can be recognized at any time after the I bit in the CCR is cleared.

When an interrupt service request is recognized, the CPU responds at the completion of the instruction

being executed. Interrupt latency varies according to the number of cycles required to complete the in-

struction. Some of the longer instructions can be interrupted and will resume normally after servicing

the interrupt.

When the CPU begins to service an interrupt, the instruction queue is cleared, the return address is cal-

culated, and then it and the contents of the CPU registers are stacked as shown in

Table 18

.

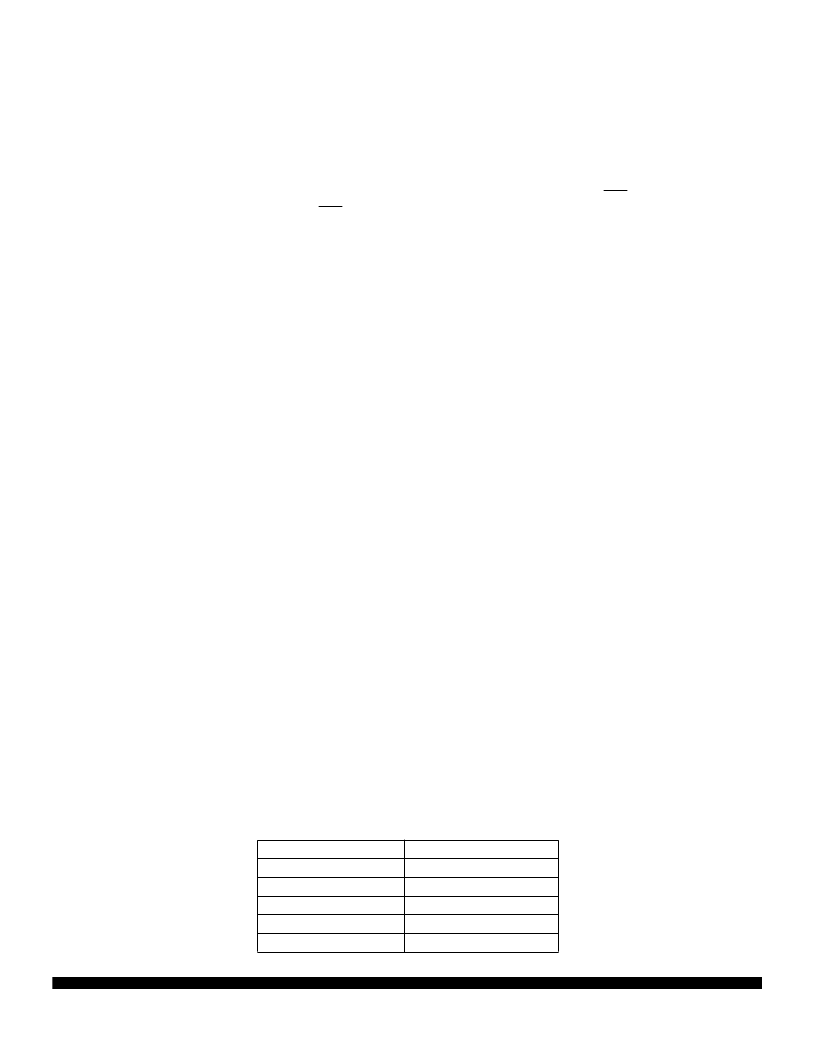

Table 18 Stacking Order on Entry to Interrupts

Memory Location

SP – 2

SP – 4

SP – 6

SP – 8

SP – 9

CPU Registers

RTN

H

: RTN

L

Y

H

: Y

L

X

H

: X

L

B : A

CCR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68C912B32FU8 | 16-Bit Microcontroller |

| MC68B912B32FU8 | 16-Bit Microcontroller |

| MC68C912B32CFU8 | 16-Bit Microcontroller |

| MC68CK338 | Highly Integrated, Low-Power, 32-Bit Microcontroller |

| MC68EC060 | 32-Bit Microprocessors.(32位微處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68B912B32FU8 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:16-Bit Microcontroller |

| MC68BOOL | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:8-BIT MICROPROCESSING UNIT (MPU) |

| MC68BOOP | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:8-BIT MICROPROCESSING UNIT (MPU) |

| MC68BOOS | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:8-BIT MICROPROCESSING UNIT (MPU) |

| MC68C812A4 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Technical Supplement MC68C812A4 3.3V Electrical Characteristics |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。