- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45222 > MC68HC05P18MDW (MOTOROLA INC) 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC05P18MDW |

| 廠商: | MOTOROLA INC |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDSO28 |

| 封裝: | SOIC-28 |

| 文件頁(yè)數(shù): | 127/144頁(yè) |

| 文件大?。?/td> | 1348K |

| 代理商: | MC68HC05P18MDW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)當(dāng)前第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)

Analog-to-Digital (A/D) Converter

A/D Status and Control Register

MC68HC(8)05P18 — Rev. 2.0

Advance Information

MOTOROLA

Analog-to-Digital (A/D) Converter

83

ADON — A/D Subsystem On But

When the A/D subsystem is turned on (ADON = 1), it requires a time,

tADON, to stabilize before accurate conversion results can be attained.

CH2-CH0 — Channel Select Bits

CH2, CH1, and CH0 form a 3-bit field which is used to select an input

to the A/D converter. Channels 0–3 correspond to port C input pins

PC6–PC3. Channels 4–6 are used for reference measurements. In

user mode channel 7 is reserved. If a conversion is attempted with

channel 7 selected the result will be $00. Table 9-1 lists the inputs

selected by bits CH0–CH3.

If the ADON bit is set and an input from channels 0–4 is selected, the

corresponding port C pin’s DDR bit will be cleared (making that port C

pin an input). If the port C data register is read while the A/D is on and

one of the shared input channels is selected using bit CH0–CH2, the

corresponding port C pin will read as a logic 0. The remaining port C pins

will read normally. To digitally read a port C pin, the A/D subsystem must

be disabled (ADON = 0) or input channels 5–7 must be selected.

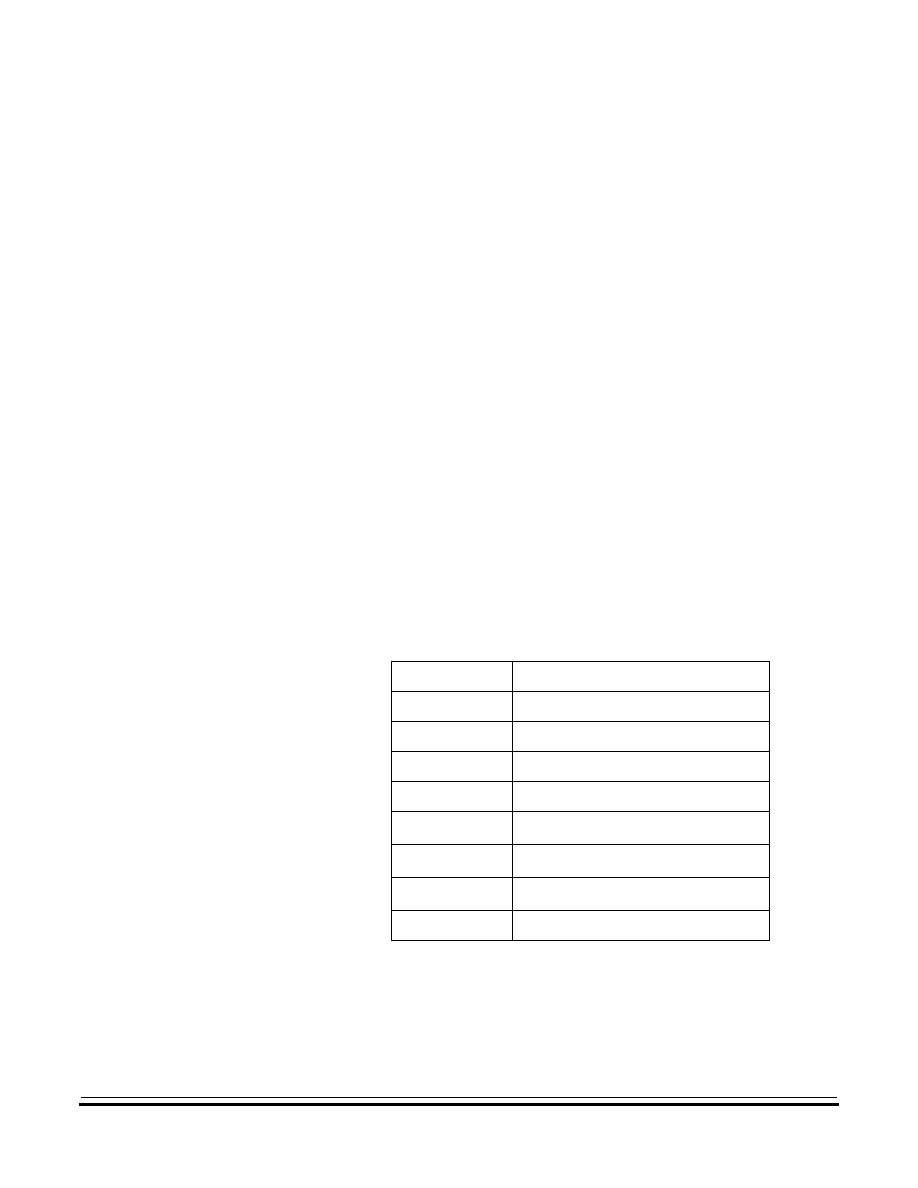

Table 9-1. A/D Multiplexer Input

Channel Assignments

Channel

Signal

0

AD0 — port C, bit 6

1

AD1 — port C, bit 5

2

AD2 — port C, bit 4

3

AD3 — port C, bit 3

4

VREFH — port C, bit 7

5

(VREFH + VSS)/2

6

VSS

7

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC05P1AP | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDIP28 |

| MC68HCL05P1ADW | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDSO28 |

| MC68HC05P2CFN | 8-BIT, MROM, MICROCONTROLLER, PQCC32 |

| MC68HC05P2FN | 8-BIT, MROM, MICROCONTROLLER, PQCC32 |

| MC68HC05P3DWR3 | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC05P1A | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification |

| MC68HC05P1ADW | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification |

| MC68HC05P1AP | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:General Release Specification |

| MC68HC05P1CDW | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:HCMOS Microcontroller Unit |

| MC68HC05P1CP | 制造商:FREESCALE 制造商全稱(chēng):Freescale Semiconductor, Inc 功能描述:HCMOS Microcontroller Unit |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。