- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25624 > MC80C52XXX-25/883 (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號: | MC80C52XXX-25/883 |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CDIP40 |

| 文件頁數(shù): | 40/83頁 |

| 文件大小: | 8336K |

| 代理商: | MC80C52XXX-25/883 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

37

8021G–AVR–03/11

ATmega329P/3290P

9.

Power Management and Sleep Modes

9.1

Overview

Sleep modes enable the application to shut down unused modules in the MCU, thereby saving-

power. The AVR provides various sleep modes allowing the user to tailor the power

consumption to the application’s requirements.

When enabled, the Brown-out Detector (BOD) actively monitors the power supply voltage during

the sleep periods. To further save power, it is possible to disable the BOD in some sleep modes.

See ”BOD Disable” on page 38 for more details.

9.2

Sleep Modes

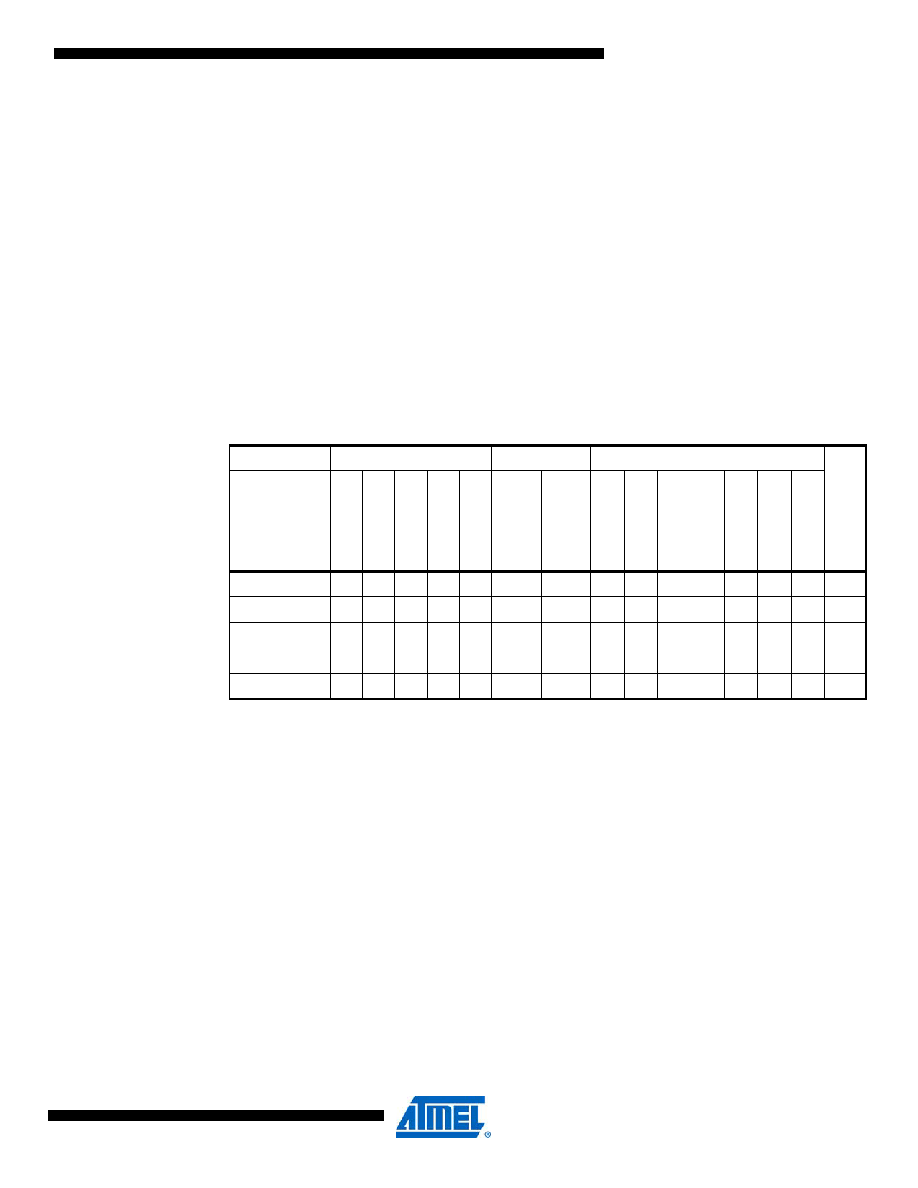

Figure 8-1 on page 27 presents the different clock systems in the ATmega329P/3290P, and

their distribution. The figure is helpful in selecting an appropriate sleep mode. Table 9-1 shows

the different sleep modes, their wake up sources and BOD disable ability.

Notes:

1. Only recommended with external crystal or resonator selected as clock source.

2. If either LCD controller or Timer/Counter2 is running in asynchronous mode.

3. For INT0, only level interrupt.

To enter any of the sleep modes, the SE bit in SMCR must be written to logic one and a SLEEP

instruction must be executed. The SM2, SM1, and SM0 bits in the SMCR Register select which

sleep mode will be activated by the SLEEP instruction. See Table 9-2 on page 42 for a

summary.

If an enabled interrupt occurs while the MCU is in a sleep mode, the MCU wakes up. The MCU

is then halted for four cycles in addition to the start-up time, executes the interrupt routine, and

resumes execution from the instruction following SLEEP. The contents of the Register File and

SRAM are unaltered when the device wakes up from sleep. If a reset occurs during sleep mode,

the MCU wakes up and executes from the Reset Vector.

Table 9-1.

Active Clock Domains and Wake-up Sources in the Different Sleep Modes.

Active Clock Domains

Oscillators

Wake-up Sources

Softw

a

re

BOD

Disd

ab

le

Sleep Mode

clk

CP

U

clk

FLAS

H

clk

IO

clk

AD

C

clk

AS

Y

Main

C

loc

k

Sour

ce

Enab

led

Tim

e

rOsc

Enab

led

INT2:

0

an

d

Pin

Chang

e

TWI

Ad

d

ress

Matc

h

Tim

e

r2

SP

M/

EE

PR

OM

Read

y

ADC

W

D

T

Interrupt

Ot

her

I/O

Idle

XXX

X

XXX

X

ADCNRM

X

X(3)

XX(2)

XXX

Power-down

X(3)

XX

X

Power-save

X

X(3)

XX

X

Standby(1)

XX(3)

XX

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C52EXXX-25:R | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQFP44 |

| MR80C32-12P883 | 8-BIT, 12 MHz, MICROCONTROLLER, CQCC44 |

| MC80C32-36SHXXX | 8-BIT, 36 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C32-20:RD | 8-BIT, 20 MHz, MICROCONTROLLER, CQFP44 |

| MQ80C52TXXX-16SHXXX:RD | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC80D21000G | 制造商:COR 功能描述:RN |

| MC80F0104 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0204 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。