- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371134 > MPC106ARX83DE (MOTOROLA INC) PCI Bridge/Memory Controller PDF資料下載

參數(shù)資料

| 型號: | MPC106ARX83DE |

| 廠商: | MOTOROLA INC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI Bridge/Memory Controller |

| 中文描述: | PCI BUS CONTROLLER, CBGA304 |

| 封裝: | 21 X 25 MM, 3.16 MM HEIGHT, 1.27 MM PITCH, CERAMIC, BGA-304 |

| 文件頁數(shù): | 22/28頁 |

| 文件大?。?/td> | 158K |

| 代理商: | MPC106ARX83DE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁

22

MPC106 PCI Bridge/Memory Controller Hardware Specifications

System Design Information

1.8 System Design Information

This section provides electrical and thermal design recommendations for successful application of the 106.

1.8.1 PLL Configuration

The 106 requires a single system clock input, SYSCLK. The SYSCLK frequency dictates the frequency of

operation for the PCI bus. An internal PLL on the MPC106 generates a master clock that is used for all of

the internal (core) logic. The master clock provides the core frequency reference and is phase-locked to the

SYSCLK input. The 60x processor, L2 cache, and memory interfaces operate at the core frequency. In the

5:2 clock mode (Rev. 4.0 only), the MPC106 needs to sample the 60x bus clock (on the LBCLAIM

configuration input) to resolve clock phasing with the PCI bus clock (SYSCLK).

The PLL is configured by the PLL[0–3] signals. For a given SYSCLK (PCI bus) frequency, the clock mode

configuration signals (PLL[0–3]) set the core frequency (and the frequency of the VCO controlling the

PLL lock). The supported core and VCO frequencies and the corresponding PLL[0–3] settings are

provided in Table 11.

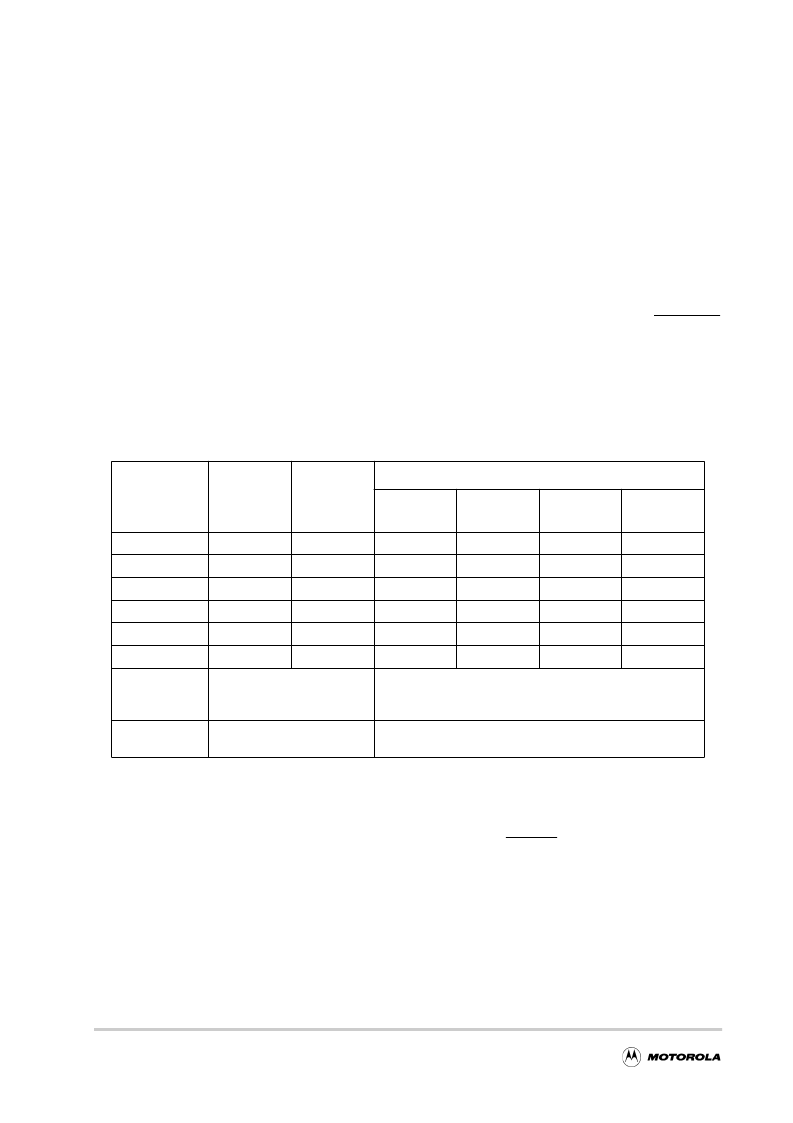

Table 11. PLL Configuration

PLL[0–3]

1

Core/SYSCL

K Ratio

VCO

Multiplier

Core Frequency (VCO Frequency) in MHz

PCI Bus

16.6 MHz

PCI Bus

20 MHz

PCI Bus

25 MHz

PCI Bus

33.3 MHz

0001

1:1

x4

—

—

—

33.3 (133)

0100

2:1

x2

—

—

—

66.6 (133)

0101

2:1

x4

33.3 (133)

40 (160)

50 (200)

—

0110

5:2

2

x2

—

—

—

83.3 (166)

0111

5:2

2

x4

41.6 (166)

—

—

—

1000

3:1

x2

—

60(120)

75 (150)

—

0011

PLL-bypass

3

PLL off

SYSCLK clocks core circuitry directly

1x core/SYSCLK ratio implied

1111

Clock off

4

PLL off

no core clocking occurs

Notes

:

1

PLL[0–3] settings not listed are reserved. Some PLL configurations may select bus, CPU, or VCO frequencies

which are not useful, not supported, or not tested. See Section 1.4.2.1, “Clock AC Specifications,” for valid

SYSCLK and VCO frequencies.

2

5:2 clock modes are only supported by MPC106 Rev 4.0; earlier revisions do not support 5:2 clock modes.

The 5:2 modes require a 60x bus clock applied to the 60x clock phase (LBCLAIM) configuration input signal

during power-on reset, hard reset, and coming out of sleep and suspend power-saving modes.

3

In PLL-bypass mode, the SYSCLK input signal clocks the internal circuitry directly, the PLL is disabled, and

the core/SYSCLK ratio is set for 1:1 mode operation. This mode is intended for factory use and third-party tool

vendors only.

Note also

: The AC timing specifications given in this document do not apply in PLL-bypass

mode.

4

In clock-off mode, no clocking occurs inside the MPC106 regardless of the SYSCLK input.

5

PLL[0-3] = 0010 (2:1 Core/SYSCLK Ratio; X8 VCO multiplier) exists on the chip but will fail to lock 50% of the

time. Therefore, this configuration should not be used and 1:1 modes between 16-25MHz are not supported.

相關PDF資料 |

PDF描述 |

|---|---|

| MPC106ARX83DG | PCI Bridge/Memory Controller |

| MPC106ARX83TE | PCI Bridge/Memory Controller |

| MPC106ARX83TG | PCI Bridge/Memory Controller |

| MPC2003SG50 | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

| MPC2002SG50 | 256KB and 512KB BurstRAM Secondary Cache Module for PowerPC - Based Systems |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC106ARX83DG | 制造商:Freescale Semiconductor 功能描述: |

| MPC106ARX83TE | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC106ARX83TG | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:PCI Bridge/Memory Controller |

| MPC-108 | 制造商:Greenlee Textron Inc 功能描述:Unspecified Tools & Accessories ADAPTER,MATING BULKHEAD |

| MPC108100J | 功能描述:厚膜電阻器 - 透孔 MPC10 10R 5% RoHS:否 制造商:Caddock 電阻:27 kOhms 容差:1 % 功率額定值:8 W 溫度系數(shù):50 PPM / C 系列:MS 端接類型:Axial 電壓額定值:2 kV 工作溫度范圍:- 15 C to + 275 C 尺寸:8.89 mm Dia. x 23.11 mm L 封裝:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。