- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25623 > MR80C52XXX-36P883R (ATMEL CORP) 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MR80C52XXX-36P883R |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| 封裝: | LCC-44 |

| 文件頁(yè)數(shù): | 71/132頁(yè) |

| 文件大小: | 10886K |

| 代理商: | MR80C52XXX-36P883R |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)當(dāng)前第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)

276

8151H–AVR–02/11

ATmega128A

24.15 Boundary-scan Description Language Files

Boundary-scan Description Language (BSDL) files describe Boundary-scan capable devices in

a standard format used by automated test-generation software. The order and function of bits in

the Boundary-scan Data Register are included in this description.

24.16 Register Description

24.16.1

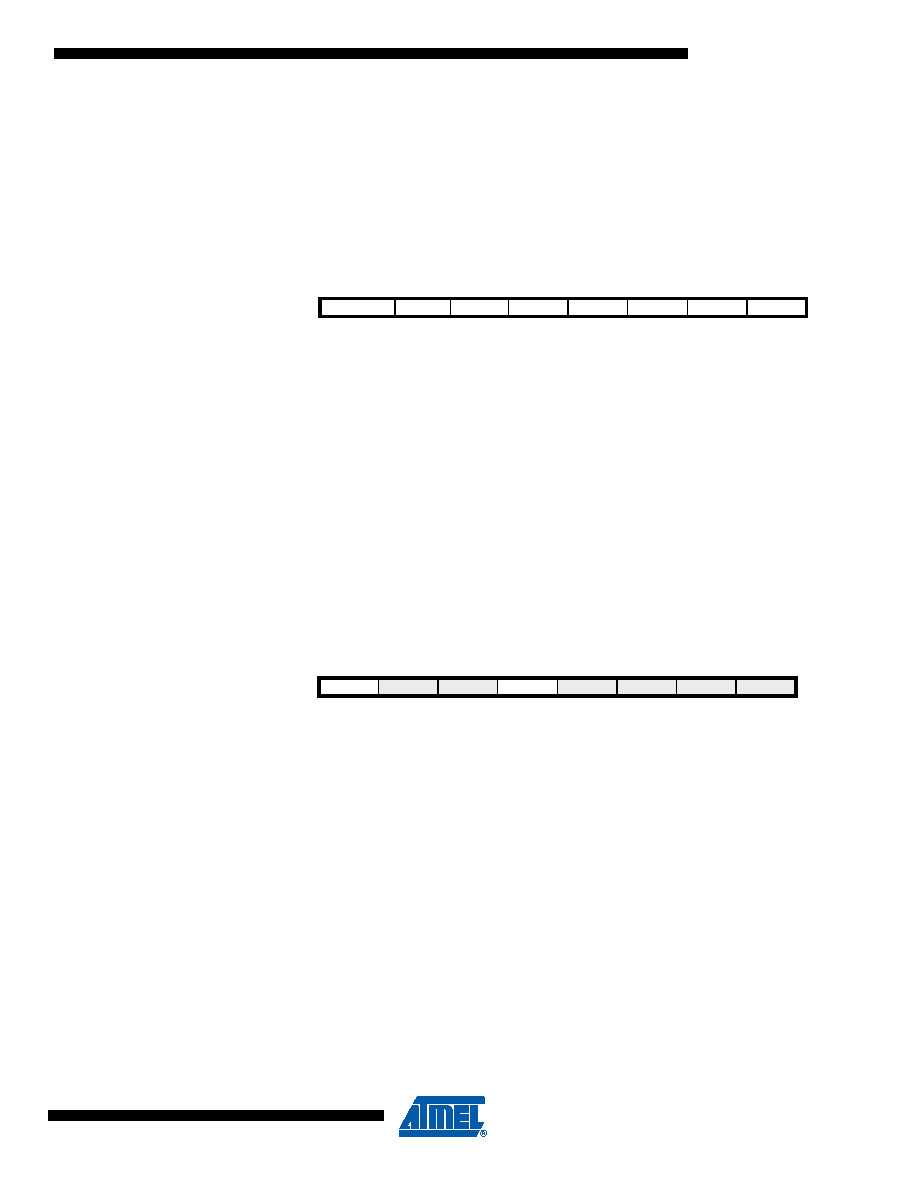

OCDR - On-chip Debug Register

The OCDR Register provides a communication channel from the running program in the micro-

controller to the debugger. The CPU can transfer a byte to the debugger by writing to this

location. At the same time, an internal flag; I/O Debug Register Dirty – IDRD – is set to indicate

to the debugger that the register has been written. When the CPU reads the OCDR Register the

7 LSB will be from the OCDR Register, while the MSB is the IDRD bit. The debugger clears the

IDRD bit when it has read the information.

In some AVR devices, this register is shared with a standard I/O location. In this case, the OCDR

Register can only be accessed if the OCDEN fuse is programmed, and the debugger enables

access to the OCDR Register. In all other cases, the standard I/O location is accessed.

Refer to the debugger documentation for further information on how to use this register.

24.16.2

MCUCSR - MCU Control and Status Register

The MCU Control and Status Register contains control bits for general MCU functions, and pro-

vides information on which reset source caused an MCU Reset.

Bit 7 – JTD: JTAG Interface Disable

When this bit is zero, the JTAG interface is enabled if the JTAGEN fuse is programmed. If this bit

is one, the JTAG interface is disabled. In order to avoid unintentional disabling or enabling of the

JTAG interface, a timed sequence must be followed when changing this bit: The application soft-

ware must write this bit to the desired value twice within four cycles to change its value.

If the JTAG interface is left unconnected to other JTAG circuitry, the JTD bit should be set to

one. The reason for this is to avoid static current at the TDO pin in the JTAG interface.

Bit 4 – JTRF: JTAG Reset Flag

This bit is set if a Reset is being caused by a logic one in the JTAG Reset Register selected by

the JTAG instruction AVR_RESET. This bit is reset by a Power-on Reset, or by writing a logic

zero to the flag.

Bit

7

6

5

4321

0

MSB/IDRD

LSB

OCDR

Read/Write

R/W

Initial Value

0

0000

0

Bit

7

65432

10

JTD

–

–JTRF

WDRF

BORF

EXTRF

PORF

MCUCSR

Read/Write

R/W

R

R/W

Initial Value

0

See Bit Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MQ80C52XXX-36SHXXX | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQFP44 |

| MC80C32E-16SHXXX:D | 8-BIT, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52XXX-36SCD | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| MD80C32-16SHXXX | 8-BIT, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR80C32E-20/883:RD | 8-BIT, 20 MHz, MICROCONTROLLER, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C86 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MR80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 80C86 16BIT CMOS 8MHZ 44PLCC - Rail/Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。