- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45398 > MSP430A018IPN (TEXAS INSTRUMENTS INC) 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | MSP430A018IPN |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQFP80 |

| 封裝: | GREEN, PLASTIC, QFP-80 |

| 文件頁數(shù): | 45/73頁 |

| 文件大小: | 1284K |

| 代理商: | MSP430A018IPN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

MSP430FG43x

MIXED SIGNAL MICROCONTROLLER

SLAS380B APRIL 2004 REVISED JUNE 2007

5

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

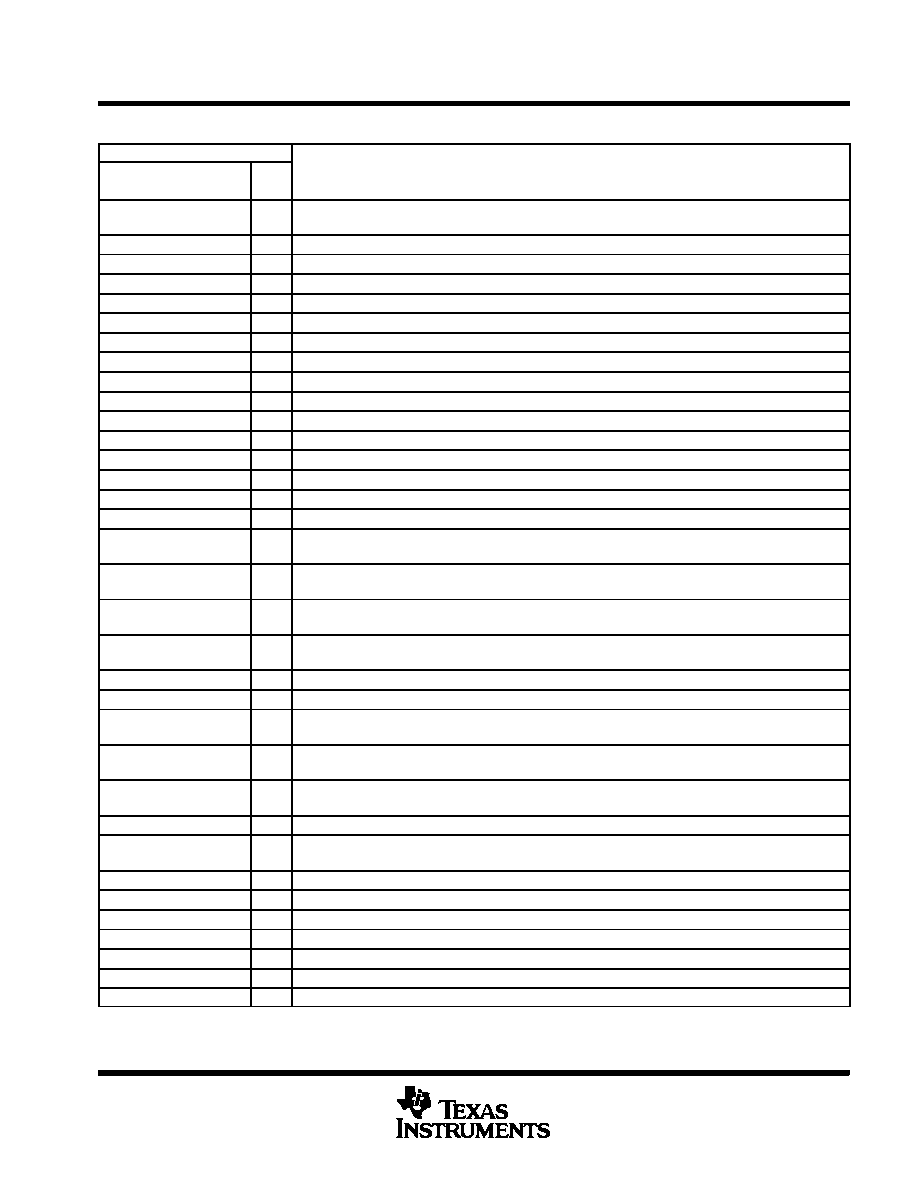

MSP430FG43x Terminal Functions (Continued)

TERMINAL

PN

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

P3.3/UCLK0/S28

40

I/O

General-purpose digital I/O / ext. clock i/p—USART0/UART or SPI mode, clock o/p—USART0/SPI mode

/ LCD segment output 28

P3.2/SOMI0/S29

41

I/O

General-purpose digital I/O / slave out/master in of USART0/SPI mode / LCD segment output 29

P3.1/SIMO0/S30

42

I/O

General-purpose digital I/O / slave out/master out of USART0/SPI mode / LCD segment output 30

P3.0/STE0/S31

43

I/O

General-purpose digital I/O / slave transmit enable-USART0/SPI mode / LCD segment output 31

COM0

44

O

Common output, COM03 are used for LCD backplanes.

P5.2/COM1

45

I/O

General-purpose digital I/O / common output, COM03 are used for LCD backplanes.

P5.3/COM2

46

I/O

General-purpose digital I/O / common output, COM03 are used for LCD backplanes.

P5.4/COM3

47

I/O

General-purpose digital I/O / common output, COM03 are used for LCD backplanes.

R03

48

I

Input port of fourth positive (lowest) analog LCD level (V5)

P5.5/R13

49

I/O

General-purpose digital I/O / input port of third most positive analog LCD level (V4 or V3)

P5.6/R23

50

I/O

General-purpose digital I/O / input port of second most positive analog LCD level (V2)

P5.7/R33

51

I/O

General-purpose digital I/O / output port of most positive analog LCD level (V1)

DVCC2

52

Digital supply voltage, positive terminal.

DVSS2

53

Digital supply voltage, negative terminal.

P2.5/URXD0

54

I/O

General-purpose digital I/O / receive data in—USART0/UART mode

P2.4/UTXD0

55

I/O

General-purpose digital I/O / transmit data out—USART0/UART mode

P2.3/TB2

56

I/O

General-purpose digital I/O / Timer_B3 CCR2.

Capture: CCI2A/CCI2B input, compare: Out2 output

P2.2/TB1

57

I/O

General-purpose digital I/O / Timer_B3 CCR1.

Capture: CCI1A/CCI1B input, compare: Out1 output

P2.1/TB0

58

I/O

General-purpose digital I/O / Timer_B3 CCR0.

Capture: CCI0A/CCI0B input, compare: Out0 output

P2.0/TA2

59

I/O

General-purpose digital I/O / Timer_A

Capture: CCI2A input, compare: Out2 output

P1.7/CA13

60

I/O

General-purpose digital I/O / Comparator_A input

P1.6/CA0

61

I/O

General-purpose digital I/O / Comparator_A input

P1.5/TACLK/

ACLK

62

I/O

General-purpose digital I/O / Timer_A, clock signal TACLK input /

ACLK output (divided by 1, 2, 4, or 8)

P1.4/TBCLK/

SMCLK

63

I/O

General-purpose digital I/O / input clock TBCLK—Timer_B3 / submain system clock SMCLK output

P1.3/TBOUTH/

SVSOUT

64

I/O

General-purpose digital I/O / switch all PWM digital output ports to high impedance—Timer_B3 TB0 to TB2

/ SVS: output of SVS comparator

P1.2/TA1

65

I/O

General-purpose digital I/O / Timer_A, Capture: CCI1A, compare: Out1 output

P1.1/TA0/MCLK

66

I/O

General-purpose digital I/O / Timer_A. Capture: CCI0B / MCLK output. Note: TA0 is only an input on this

pin / BSL receive

P1.0/TA0

67

I/O

General-purpose digital I/O / Timer_A. Capture: CCI0A input, compare: Out0 output / BSL transmit

XT2OUT

68

O

Output terminal of crystal oscillator XT2

XT2IN

69

I

Input port for crystal oscillator XT2. Only standard crystals can be connected.

TDO/TDI

70

I/O

Test data output port. TDO/TDI data output or programming data input terminal

TDI/TCLK

71

I

Test data input or test clock input. The device protection fuse is connected to TDI/TCLK.

TMS

72

I

Test mode select. TMS is used as an input port for device programming and test.

TCK

73

I

Test clock. TCK is the clock input port for device programming and test.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSP430A059IRTDT | 16-BIT, FLASH, 8 MHz, RISC MICROCONTROLLER, PQCC64 |

| MSP430AFE233IPW | 16-BIT, FLASH, RISC MICROCONTROLLER, PDSO24 |

| MSP430AFE252IPW | 16-BIT, FLASH, RISC MICROCONTROLLER, PDSO24 |

| MSP430AFE231IPW | 16-BIT, FLASH, RISC MICROCONTROLLER, PDSO24 |

| MSP430BT5190IZQW | RISC MICROCONTROLLER, PBGA113 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSP430A041IRTDR | 功能描述:16位微控制器 - MCU Ultra low Pwr MCU RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MSP430A059IRTDR | 功能描述:16位微控制器 - MCU Ultra low Pwr MCU RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MSP430A059IRTDT | 功能描述:16位微控制器 - MCU Ultra low Pwr MCU RoHS:否 制造商:Texas Instruments 核心:RISC 處理器系列:MSP430FR572x 數(shù)據(jù)總線寬度:16 bit 最大時(shí)鐘頻率:24 MHz 程序存儲(chǔ)器大小:8 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:VQFN-40 安裝風(fēng)格:SMD/SMT |

| MSP430A060CY | 制造商:Texas Instruments 功能描述:6 CHANNEL LOW COST PWM |

| MSP430A061IDAR | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。