- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224506 > MT58L512L18DT-10IT 512K X 18 CACHE SRAM, 5 ns, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | MT58L512L18DT-10IT |

| 元件分類: | SRAM |

| 英文描述: | 512K X 18 CACHE SRAM, 5 ns, PQFP100 |

| 封裝: | PLASTIC, MS-026BHA, TQFP-100 |

| 文件頁(yè)數(shù): | 3/31頁(yè) |

| 文件大?。?/td> | 613K |

| 代理商: | MT58L512L18DT-10IT |

第1頁(yè)第2頁(yè)當(dāng)前第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)

11

8Mb: 512K x 18, 256K x 32/36 3.3V I/O, Pipelined, DCD SyncBurst SRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT58L512L18D_C.p65 – Rev. 6/01

2001, Micron Technology, Inc.

8Mb: 512K x 18, 256K x 32/36

3.3V I/O, PIPELINED, DCD SYNCBURST SRAM

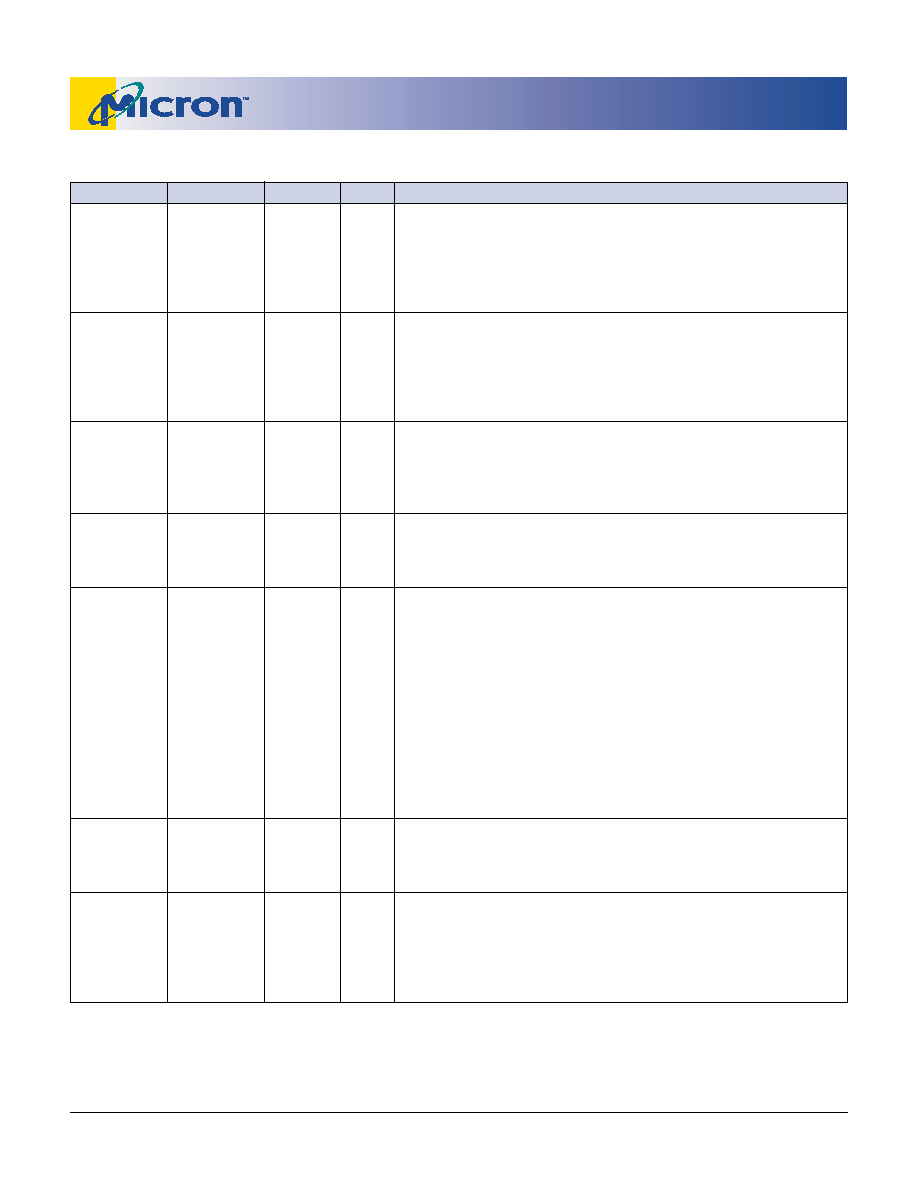

FBGA PIN DESCRIPTIONS (continued)

x18

x32/x36

SYMBOL

TYPE

DESCRIPTION

9A

ADV#

Input

Synchronous Address Advance: This active LOW input is used to

advance the internal burst counter, controlling burst access after

the external address is loaded. A HIGH on ADV# effectively causes

wait states to be generated (no address advance). To ensure use of

correct address during a WRITE cycle, ADV# must be HIGH at the

rising edge of the first clock after an ADSP# cycle is initiated.

9B

ADSP#

Input

Synchronous Address Status Processor: This active LOW input

interrupts any ongoing burst, causing a new external address to be

registered. A READ is performed using the new address,

independent of the byte write enables and ADSC#, but dependent

upon CE#, CE2, and CE2#. ADSP# is ignored if CE# is HIGH. Power-

down state is entered if CE2 is LOW or CE2# is HIGH.

8A

ADSC#

Input

Synchronous Address Status Controller: This active LOW input

interrupts any ongoing burst, causing a new external address to be

registered. A READ or WRITE is performed using the new address if

CE# is LOW. ADSC# is also used to place the chip into power-down

state when CE# is HIGH.

1R

MODE

Input

Mode: This input selects the burst sequence. A LOW on this

(LB0#)

input selects “l(fā)inear burst.” NC or HIGH on this input selects

“interleaved burst.” Do not alter input state while device is

operating.

(a) 10J, 10K,

DQa

Input/ SRAM Data I/Os: For the x18 version, Byte “a” is associated DQas;

10L, 10M, 11D, 10L, 10M, 11J,

Output Byte “b” is associated with DQbs. For the x32 and x36 versions,

11E, 11F, 11G 11K, 11L, 11M

Byte “a” is associated with DQas; Byte “b” is associated with DQbs;

Byte “c” is associated with DQcs; Byte “d” is associated with DQds.

(b) 1J, 1K,

(b) 10D, 10E,

DQb

Input data must meet setup and hold times around the rising edge

1L, 1M, 2D,

10F, 10G, 11D,

of CLK.

2E, 2F, 2G

11E, 11F, 11G

(c) 1D, 1E,

DQc

1F, 1G, 2D,

2E, 2F, 2G

(d) 1J, 1K, 1L,

DQd

1M, 2J, 2K,

2L, 2M

11C

11N

NF/DQPa

NF/

No Funciton/Parity Data I/Os: On the x32 version, these are No

1N

11C

NF/DQPb

I/O

Function (NF). On the x18 version, Byte “a” parity is DQPa; Byte “b”

–

1C

NF/DQPc

parity is DQPb. On the x36 version, Byte “a” parity is DQPa; Byte

–

1N

NF/DQPd

“b” parity is DQPb; Byte “c” parity is DQPc; Byte “d” parity is DQPd.

1H, 4D, 4E, 4F, 1H, 4D, 4E, 4F,

VDD

Supply Power Supply: See DC Electrical Characteristics and Operating

4G, 4H, 4J,

Conditions for range.

4K, 4L, 4M,

8D, 8E, 8F,

8G, 8H, 8J,

8K, 8L, 8M

(continued on next page)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT58L512L18PB-6IT | 512K X 18 STANDARD SRAM, 3.5 ns, PBGA119 |

| MT58L512L18PS-7.5IT | 512K X 18 CACHE SRAM, 4 ns, PQFP100 |

| MT78740 | RELAY SOCKET |

| MT78745 | RELAY SOCKET |

| MT9KDF12872PZ-1G6XX | 128M X 72 DDR DRAM MODULE, DMA240 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT58L512L18DT-7.5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L512L18F | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:8Mb: 512K x 18, 256K x 32/36 FLOW-THROUGH SYNCBURST SRAM |

| MT58L512L18FF-10 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L512L18FF-10IT | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

| MT58L512L18FF-7.5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Micron Technology Inc 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。