- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359235 > MT90883 (Zarlink Semiconductor Inc.) TDM to Packet Processors PDF資料下載

參數(shù)資料

| 型號: | MT90883 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | TDM to Packet Processors |

| 中文描述: | TDM到分組處理器 |

| 文件頁數(shù): | 48/97頁 |

| 文件大?。?/td> | 702K |

| 代理商: | MT90883 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁

MT90880/1/2/3

Data Sheet

48

Zarlink Semiconductor Inc.

Programmable size jitter buffer size

6.4 Operation of the WAN Receive Block

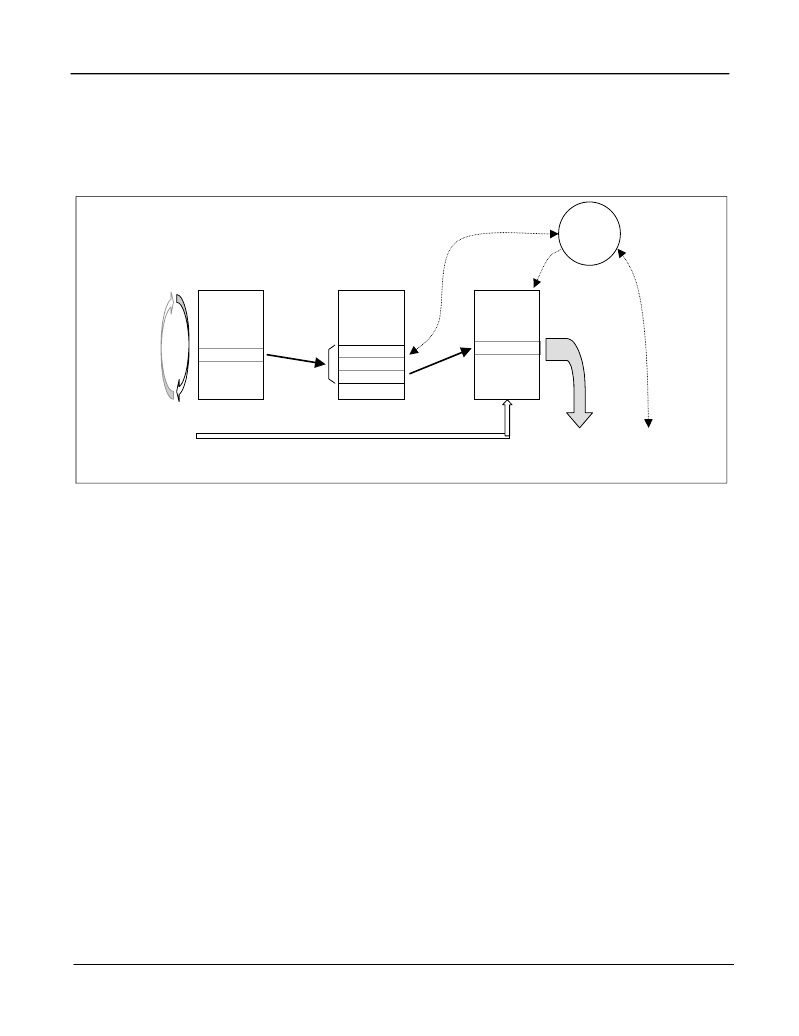

The diagram in Figure 24 shows a simplified, conceptual diagram of the WAN Receive Controller, demonstrating

the principles of its operation.

Figure 24 - Operation of the WAN Receive Controller

The WAN Receive controller receives constant bit rate TDM traffic from the WAN Interface. This interface

continually presents new timeslot data at the input, together with an indication of the timeslot and stream the

data is taken from. The

timeslot pointer

is used to look up the identity of the context that the timeslot is assigned

to in the

context lookup table

. This table is programmed by the use to contain the mapping of timeslots into

contexts.

The

context ID

is then used to look up information about the context from the

context memory.

This includes a

pointer to the

data cache

where the timeslot data for the context is assembled prior to being stored in the

external packet memory. The context memory also includes a number of user programmable fields controlling

the context operation, such as packet payload length, context update and context teardown.

The

context control state machine

controls the allocation of the data cache and other information related to the

context. It also handles the writing of the data cache contents into the external packet memory, requesting

memory access from the Memory Management Unit.

The WAN Transmit Controller functions in a similar manner, but with the data flow in reverse. The control flow

remains driven by the constant bit rate of the WAN Interface.

6.4.1 Context Control in the WAN Receive/Transmit Controllers

The Context Look-Up Table is the key to the control of contexts in both the WAN Receive and WAN Transmit

Controllers. This contains the mapping of individual channels into contexts, and also provides the capability to

program modifications to contexts without affecting existing channels. The fields within the context lookup table are

shown in Figure 25.

circulating

timeslot

pointer

Context ID

context

lookup

table

context control

state

cache address

context

memory

cache buffer

data cache

Context

control

state

machine

to external

packet memory

timeslot

data

to memory

manager

相關PDF資料 |

PDF描述 |

|---|---|

| MT91600 | Programmable SLIC |

| MT91600AN | Programmable SLIC |

| MT91600AN1 | Programmable SLIC |

| MT91600ANR | Programmable SLIC |

| MT91600ANR1 | Programmable SLIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT90883A | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT90883A/IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT90883BP1N | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT90883IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT9088IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

發(fā)布緊急采購,3分鐘左右您將得到回復。