- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369957 > PD6710 (Intel Corp.) ISA-to-PC-Card (PCMCIA) Controllers PDF資料下載

參數(shù)資料

| 型號: | PD6710 |

| 廠商: | Intel Corp. |

| 英文描述: | ISA-to-PC-Card (PCMCIA) Controllers |

| 中文描述: | ISA -到- PC卡(PCMCIA)的控制器 |

| 文件頁數(shù): | 91/138頁 |

| 文件大小: | 723K |

| 代理商: | PD6710 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁當(dāng)前第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁

ISA-to-PC-Card (PCMCIA) Controllers

—

PD6710/

’

22

Datasheet

91

13.0

Using GPSTB Pins for External Port Control

(PD6722 only)

The PD6722 provides pins that can be programmed to function as general-purpose strobes to

external latches or buffers, allowing them to serve as read ports or write ports mapped into the

PD6722 register set.

Configuring a GPSTB pin as a read port allows an easy way to read additional card status such as

VS1# and VS2# levels, a card socket microswitch status, a card port cover microswitch status, card

eject solenoid position status, or general system signal status.

Configuring a GPSTB pin as a write port allows an easy way to control additional features such as

card-state LEDs, card mechanism solenoids, or motor eject mechanisms.

13.1

Control of GPSTB Pins

The

Extension Control 2

register controls the GPSTB pins.

For the PD6722, the A_GPSTB pin is controlled by the

Extension Control 2

register at Socket A

(index 2Fh, extended index 0Bh), and the B_GPSTB pin is controlled by the

Extension Control 2

register at Socket B (index 6Fh, extended index 0Bh).

The following table summarizes how the GPSTB pins are configured and how data is accessed

from external ports created by using a GPSTB pin to control an external read or write port.

Programming the Extension Control 2 Register

There is one

Extension Control 2

register per GPSTB pin. Each register has identical GPSTB

control bits, as follows. See also the description of this register in

“

Extension Control 2 (PD6722

only)

”

on page 83

.

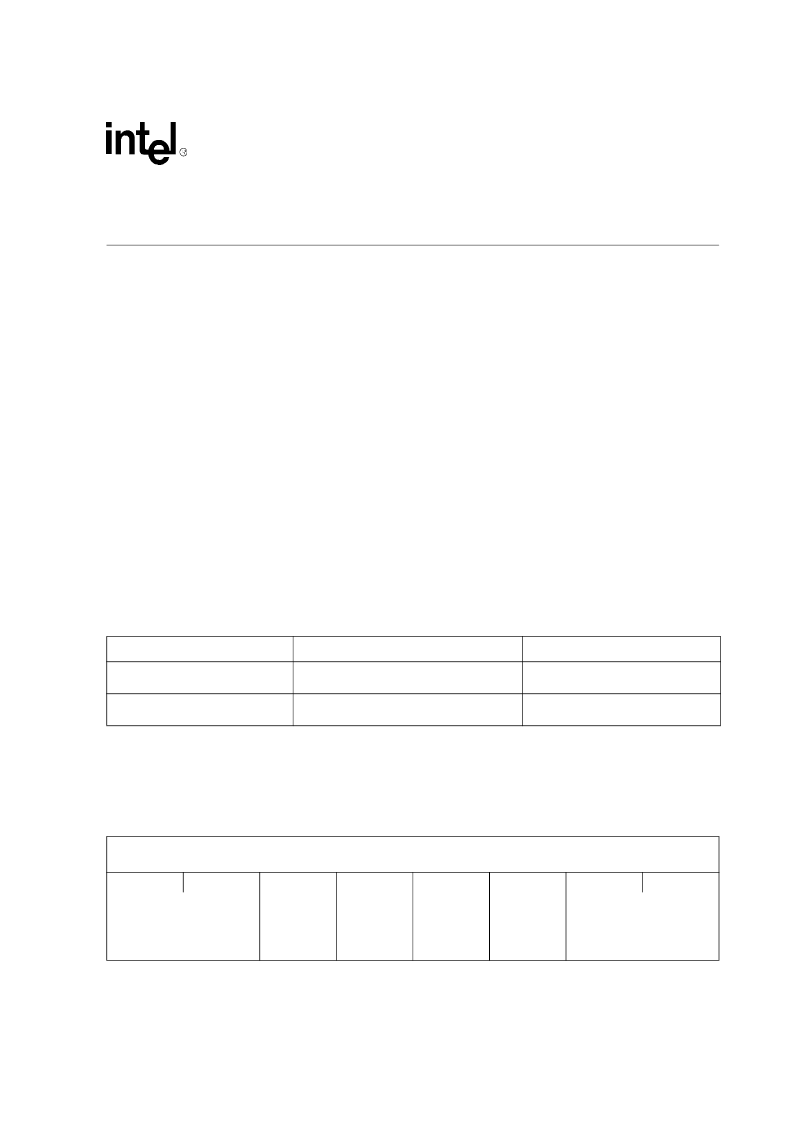

Table 18. Registers for Control and Data of GPSTB Pins

Pin Name

GPSTB Control Access

External Port Data Access

A_GPSTB (PD6722)

Set register 2E to 0Bh,

access

Extension Control 2

register at 2F

Set register 2E to 0Ah,

access

External Data

register at 2F

B_GPSTB (PD6722)

Set register 6E to 0Bh,

access

Extension Control 2

register at 6F

Set register 6E to 0Ah,

access

External Data

register at 6F

Register Name:

Extension Control 2

Index:

2Fh and 6Fh

Extended Index:

0Bh

Register Per:

socket

Register Compatibility Type:

ext.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Reserved

Active-high

GPSTB

GPSTB on

IOW*

GPSTB on

IOR*

Totem-pole

GPSTB

Reserved

RW:00

RW:0

RW:0

RW:0

RW:0

RW:00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PD7-20-70A | Analog IC |

| PD7-80-70A | Analog IC |

| PD7-40-70A | Analog IC |

| PD700A7 | Optoelectronic |

| PDA2446-B-AP | Analog Pigtailed PIN Photodiodes |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD67108AM | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:24-Channel PoE AF and AT DIMM |

| PD67108MAC-0212 | 制造商:Microsemi Corporation 功能描述:POE PSE MODULES - Bulk |

| PD67108MAC-GGGG | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:24-Channel PoE AF and AT DIMM |

| PD67108MDC-0212 | 制造商:Microsemi Corporation 功能描述:POE PSE MODULES - Bulk |

| PD67108MDC-GGGG | 制造商:MICROSEMI 制造商全稱:Microsemi Corporation 功能描述:24-Channel PoE AF and AT DIMM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。