- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367897 > PE3293 (Electronic Theatre Controls, Inc.) 1.8GHz/550MHz Dual Fractional-N Ultra-Low Spurious PLL for Frequency Synthesis PDF資料下載

參數(shù)資料

| 型號: | PE3293 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 1.8GHz/550MHz Dual Fractional-N Ultra-Low Spurious PLL for Frequency Synthesis |

| 中文描述: | 1.8GHz/550MHz雙分數(shù)N超低的雜散鎖相環(huán)頻率合成 |

| 文件頁數(shù): | 3/18頁 |

| 文件大小: | 266K |

| 代理商: | PE3293 |

PE3293

Product Specification

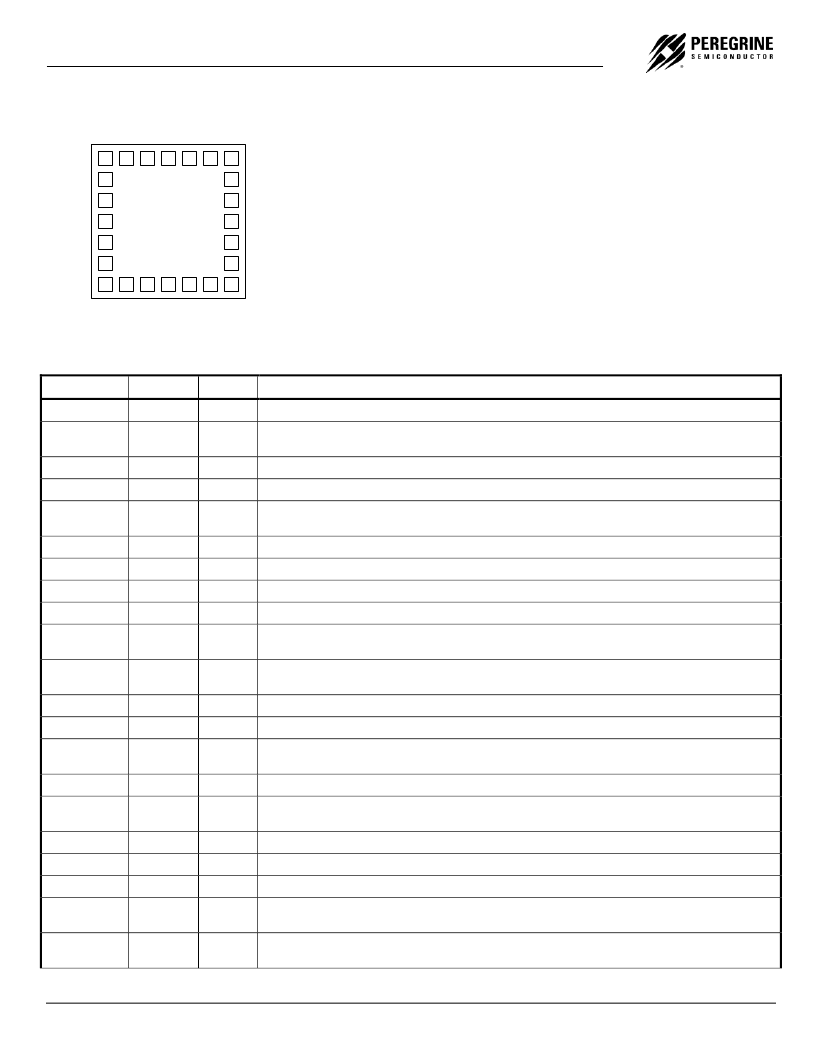

Figure 3. Pin Configuration: 24-Pin BCC (Top View)

PEREGRINE SEMICONDUCTOR CORP.

|

http://www.peregrine-semi.com

Copyright

Peregrine Semiconductor Corp. 2003

Page 3 of 18

Table 2. Pin Descriptions

Pin No.

Pin Name

Type

Description

1

N / C

No connect.

2

CP1

Output

Internal charge-pump output from PLL1 for connection to a loop filter for driving the input of an external

VCO.

3

GND

Ground

4

f

in

1

Input

Prescaler input from the PLL1 (RF) VCO. Maximum frequency is 1.8 GHz.

5

Dec1

Power supply decoupling pin for PLL1. A capacitor should be placed as close as possible to this pin and be

connected directly to the ground plane.

6

V

DD1

PLL1 prescaler power supply (FlexiPower 1).

7

N / C

No connect.

8

f

r

Input

Reference frequency input.

9

GND

Ground.

10

f

o

LD

Output

Multiplexed output of the PLL1 and PLL2 main counters or reference counters, Lock Detect signals, and

data out of the shift register. CMOS output (see Table 11, f

o

LD Programming Truth Table).

11

Clock

Input

CMOS clock input. Serial data for the various counters is clocked in on the rising edge into the 21-bit shift

register.

12

Data

Input

Binary serial data input. CMOS input data entered MSB first. The two LSBs are the control bits.

13

N / C

No connect.

14

LE

Input

Load Enable CMOS input. When LE is high, data word stored in the 21-bit serial shift register is loaded into

one of the four appropriate latches (as assigned by the control bits).

15

V

DD2

PLL2 prescaler power supply. 3.3 kohm resistor to V

DD

.

16

Dec2

Power supply decoupling pin for PLL2. A capacitor should be placed as close as possible to this pin and be

connected directly to the ground plane.

17

f

in

2

Input

Prescaler input from the PLL2 (IF) VCO. Maximum frequency is 550MHz.

18

GND

Ground.

19

N / C

No connect.

20

CP2

Output

Internal charge-pump output for PLL2. For connection to a loop filter for driving the input of an external

VCO.

21

V

DD

(Note 1)

Power supply voltage input. Input may range from 2.7 V to 3.3 V. A bypass capacitor should be placed as

close as possible to this pin and be connected directly to the ground plane.

N/C

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

21

22

23

24

CP2

V

DD

V

DD

N/C

V

DD

N/C

N/C

Data

Clock

f

o

LD

GND

f

r

N/C

GND

f

in

2

Dec2

V

DD2

LE

CP1

GND

f

in

1

DEC1

V

DD1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PE4-SERIES | Optoelectronic |

| PC8-SERIES | Optoelectronic |

| PE8-SERIES | Optoelectronic |

| PC4-SERIES | Optoelectronic |

| PE4140 | Ultra-High Linearity Broadband Quad MOSFET Array |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PE3293LF | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG196A/U MCX PLUG TO MCX PLUG |

| PE3295 | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG174/U MCX PLUG TO MCX PLUG TO MCX PLUG |

| PE3297 | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U MCX PLUG TO MCX PLUG |

| PE3297LF | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U MCX PLUG TO MCX PLUG TO MCX PLUG(LEAD FREE SOLDER) |

| PE3299LF | 制造商:PASTERNACK 制造商全稱:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG188A/U MCX PLUG RIGHT ANGLE TO MCX PLUG RIGHT ANGLE(LEAD FREE) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。