- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369993 > pentium processor with MMX (Intel Corp.) 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | pentium processor with MMX |

| 廠商: | Intel Corp. |

| 英文描述: | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

| 中文描述: | 32位MMX技術(shù)(32位帶MMX公司的技術(shù)處理器處理器) |

| 文件頁(yè)數(shù): | 16/51頁(yè) |

| 文件大小: | 479K |

| 代理商: | PENTIUM PROCESSOR WITH MMX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)

PENTIUM PROCESSOR WITH MMX TECHNOLOGY

E

16

5/23/97 10:47 AM 24318502.DOC

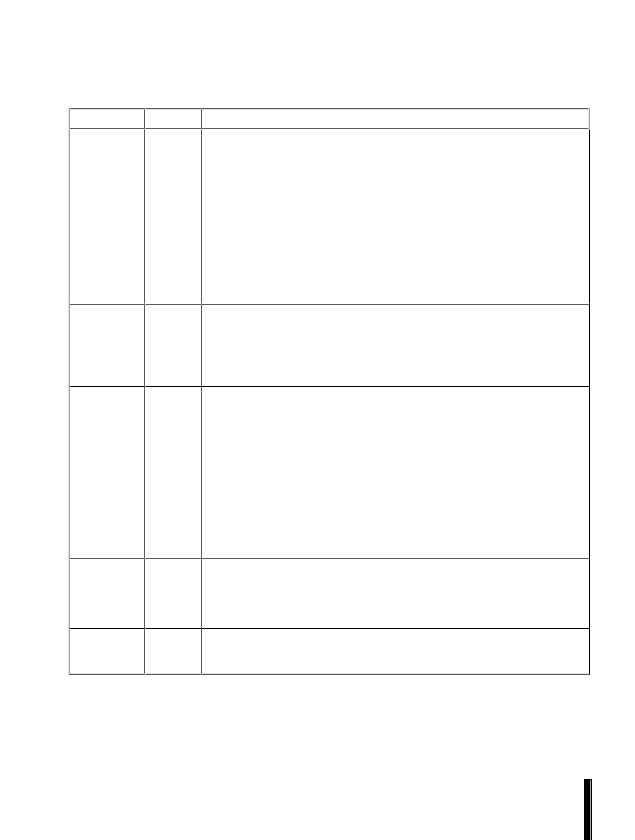

Table 2. Quick Pin Reference

(Cont’d)

Symbol

Type

Name and Function

BUSCHK#

I

The

bus check

input allows the system to signal an unsuccessful completion of a

bus cycle. If this pin is sampled active, the Pentium processor with MMX

technology will latch the address and control signals in the machine check

registers. If, in addition, the MCE bit in CR4 is set, the Pentium processor with

MMX technology will vector to the machine check exception.

NOTE:

To assure that BUSCHK# will always be recognized, STPCLK# must be

deasserted any time BUSCHK# is asserted by the system, before the system

allows another external bus cycle. If BUSCHK# is asserted by the system for a

snoop cycle while STPCLK# remains asserted, usually (if MCE=1) the processor

will vector to the exception after STPCLK# is deasserted. But if another snoop to

the same line occurs during STPCLK# assertion, the processor can lose the

BUSCHK# request.

CACHE#

O

For Pentium processor with MMX technology-initiated cycles the

cache

pin

indicates internal cacheability of the cycle (if a read), and indicates a burst write

back cycle (if a write). If this pin is driven inactive during a read cycle, the Pentium

processor with MMX technology will not cache the returned data, regardless of the

state of the KEN# pin. This pin is also used to determine the cycle length (number

of transfers in the cycle).

CLK

I

The

clock

input provides the fundamental timing for the Pentium processor with

MMX technology. Its frequency is the operating frequency of the Pentium

processor with MMX technology external bus, and requires TTL levels. All

external timing parameters except TDI, TDO, TMS, TRST#, and PICD0-1 are

specified with respect to the rising edge of CLK.

This pin is 3.3V-tolerant-only on the Pentium processor with MMX technology.

Please refer to the Pentium

Processor Family Developer’s Manual

(Order

Number 241428) for the CLK and PICCLK signal quality specification.

NOTE:

It is recommended that CLK begin toggling within 150 ms after V

CC

reaches its

proper operating level. This recommendation is to ensure long-term reliability of

the device.

CPUTYP

I

CPU type

distinguishes the Primary processor from the Dual processor. In a

single processor environment, or when the Pentium processor with MMX

technology is acting as the Primary processor in a dual processing system,

CPUTYP should be strapped to V

SS

. The Dual processor should have CPUTYP

strapped to V

CC3

.

D/C#

O

The

data/code

output is one of the primary bus cycle definition pins. It is driven

valid in the same clock as the ADS# signal is asserted. D/C# distinguishes

between data and code or special cycles.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動(dòng)模塊和MMX技術(shù)CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

| PESDXL4UG | Low capacitance quadruple ESD protection diode array in SOT353 package |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱(chēng):Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。