- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄369993 > pentium processor with MMX (Intel Corp.) 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) PDF資料下載

參數(shù)資料

| 型號(hào): | pentium processor with MMX |

| 廠商: | Intel Corp. |

| 英文描述: | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

| 中文描述: | 32位MMX技術(shù)(32位帶MMX公司的技術(shù)處理器處理器) |

| 文件頁(yè)數(shù): | 6/51頁(yè) |

| 文件大小: | 479K |

| 代理商: | PENTIUM PROCESSOR WITH MMX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)

PENTIUM PROCESSOR WITH MMX TECHNOLOGY

E

6

5/23/97 10:47 AM 24318502.DOC

Branch

Target

Buffer

Code Cache

16 KBytes

ROM

Control Unit

Generate

(U Pipeline)

Address

(V Pipeline)

Data Cache

16 KBytes

128

TLB

TLB

Prefetch

Address

Prefetch Buffers

Instruction Decode

Instruction

Pointer

Integer Register File

Barrel Shifter

32

32

32

32

32

32

Page

Unit

Bus

Unit

Bus

Control

6Data

Bus

32-Bit

64

Control

Register File

Add

Multiply

Divide

Floating

Point

Unit

Control

80

80

(U ALU

(V Pipeline)

Branch Verif.

& Target Addr

32

Data

Bus

MMX

TM

Unit

V-Pipeline

Connection

U-Pipeline

Connection

Data

Control

APIC

Control

DP

Logic

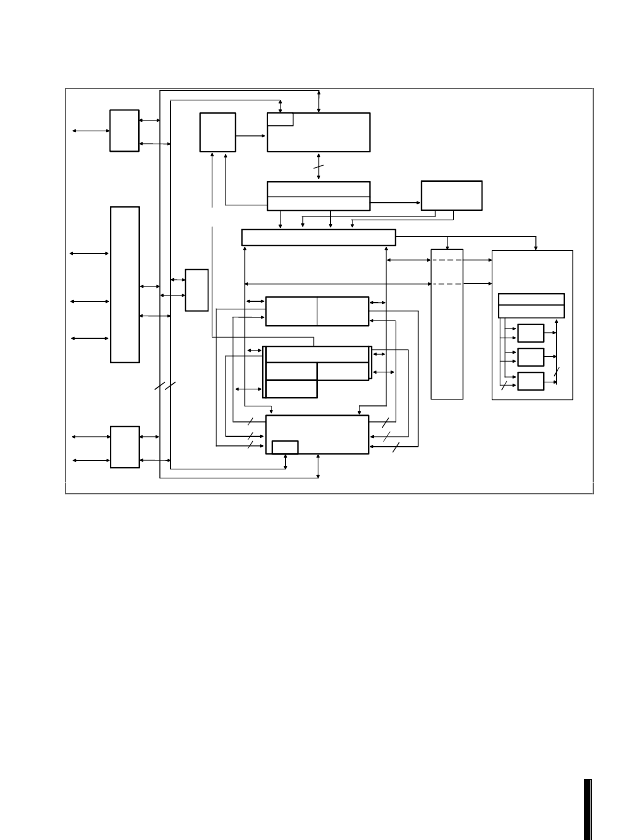

Figure 1. Pentium

Processor with MMX Technology Block Diagram

The separate code and data caches are shown. The

data cache has two ports, one for each of the two

pipes (the tags are triple ported to allow simultaneous

inquire cycles). The data cache has a dedicated

Translation Lookaside Buffer (TLB) to translate linear

addresses to the physical addresses used by the

data cache.

The code cache, branch target buffer and prefetch

buffers are responsible for getting raw instructions

into the execution units of the Pentium processor.

Instructions are fetched from the code cache or from

the external bus. Branch addresses are remembered

by the branch target buffer. The code cache TLB

translates linear addresses to physical addresses

used by the code cache.

The decode unit decodes the prefetched instructions

so the Pentium processors can execute the

instruction. The control ROM contains the microcode

which controls the sequence of operations that must

be performed to implement the Pentium processor

architecture. The control ROM unit has direct control

over both pipelines.

The Pentium processors contain a pipelined floating-

point unit that provides a significant floating-point

performance advantage over previous generations of

processors.

Symmetric dual processing in a system is supported

with two Pentium processors. The two processors

appear to the system as a single Pentium processor.

Operating systems with dual processing support

properly schedule computing tasks between the two

processors. This scheduling of tasks is transparent

to software applications and the end-user. Logic built

into the processors support a "glueless" interface for

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium processor | 32 Bit Processor With MMX And Mobile Module(32位帶移動(dòng)模塊和MMX技術(shù)CPU) |

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

| PESDXL4UG | Low capacitance quadruple ESD protection diode array in SOT353 package |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。