- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > pentium processor (Intel Corp.) 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術(shù)CPU) PDF資料下載

參數(shù)資料

| 型號: | pentium processor |

| 廠商: | Intel Corp. |

| 英文描述: | 32 Bit Processor With MMX And Mobile Module(32位帶移動模塊和MMX技術(shù)CPU) |

| 中文描述: | 32位處理器MMX和移動模塊(32位帶移動模塊和MMX公司技術(shù)的CPU) |

| 文件頁數(shù): | 25/35頁 |

| 文件大?。?/td> | 550K |

| 代理商: | PENTIUM PROCESSOR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

E

INTEL PENTIUM PROCESSOR WITH MMX TECHNOLOGY MOBILE MODULE

25

9/19/97 1:03 PM SPEIDEN_.DOC

3.4.3.

VOLTAGE SIGNAL DEFINITION AND SEQUENCING

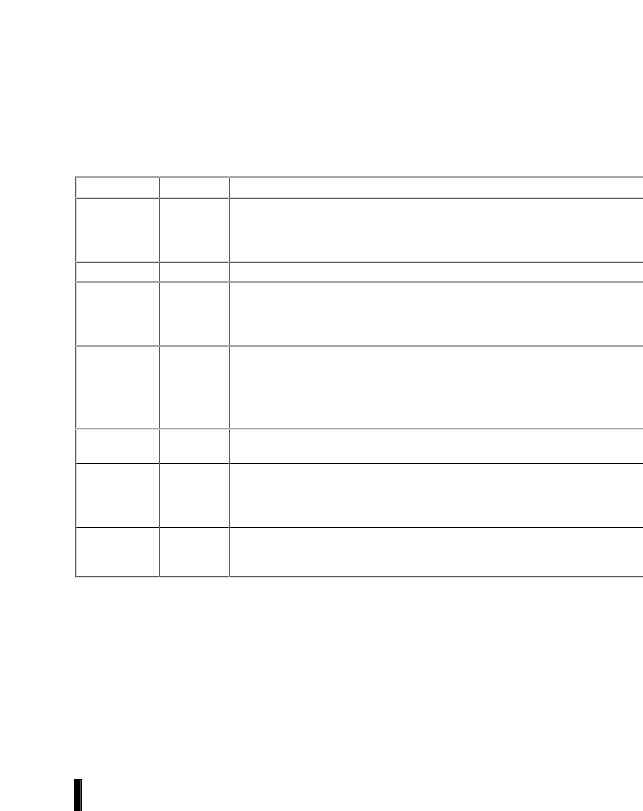

Table 13. Voltage Signal Definitions and Sequences

Signal

Source

Definitions and Sequences

V_DC

I/O Module

DC voltage driven from the power supply and is required to be between 5V and 20V DC +5%

(maximum peak voltage is 21.1V including ripple). V_DC powers the Processor Module’s DC-to-DC

converter for processor core and I/O voltages. The Intel Mobile Module can not be inserted or

removed while V_DC is powered on.

V_3

I/O Module

V_3 is supplied by the I/O Module; the MTXC uses it during the Suspend to DRAM state.

V_3S/V_5S

I/O Module

V_3S/V_5S are supplied by the I/O Module for the processor, MTXC, and cache devices. Each

must be powered off during system Suspend-to-DRAM and Suspend-to-Disk states, typically this

signal is switched by a FET switch. V_5S must be provided for the processor module voltage

regulator as well as the MTXC.

VR_ON

I/O Module

Enables the Processor Module’s voltage regulator circuit. When driven active high (3.3V) the voltage

regulator circuit on the Processor Module is activated.

CAUTION: To meet the processor specification of core (V_CORE) and I/O voltages (V_3S) being

powered on within 100ms of each other, the I/O module should subtract 6ms for the maximum

latency of VR_ON to V_CORE of the voltage regulator on the Processor Module.

V_CORE

Processor

Module Only

A result of VR_ON being asserted, V_CORE is an output of the DC-DC regulator on the Processor

Module and is driven to the appropriate voltage level of the processor: 2.5, 2.9, or 3.3V.

VR_PWRGD

Processor

Module

Upon sampling the voltage level of V_CORE for the processor’, minus tolerances for ripple,

VR_PWRGD is driven active high (3.3V) for the I/O Module to sample prior to providing PWROK to

the PIIX4. If VR_PWRGD is not sampled active within 1 second of the assertion of VR_ON the I/O

Module should deassert VR_ON.

V_CPUIO

Processor

Module

V_CPUIO is 3.3V or 2.5V depending on the processor type. The I/O Module uses this voltage to

power the PIIX4-to-processor interface circuitry, as well as the HCLK_(0:1) drivers for the

SDRAM/OEM processor clock.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PESD0603-140 | Raychem Overvoltage Devices |

| PESD5V2S18U | ESD protection array |

| PESDXL4UW | Low capacitance quadruple ESD protection array |

| PESDXL4UG | Low capacitance quadruple ESD protection diode array in SOT353 package |

| PESDXU1UT | Ultra low capacitance ESD protection diode in SOT23 package |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。