- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370005 > PLDC20G10B (Cypress Semiconductor Corp.) CMOS Generic 24-Pin Reprogrammable Logic Device PDF資料下載

參數(shù)資料

| 型號: | PLDC20G10B |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | CMOS Generic 24-Pin Reprogrammable Logic Device |

| 中文描述: | 的CMOS通用24引腳可編程邏輯器件 |

| 文件頁數(shù): | 3/14頁 |

| 文件大小: | 393K |

| 代理商: | PLDC20G10B |

USE ULTRA37000 FOR

ALL NEW DESIGNS

PLDC20G10B

PLDC20G10

Document #: 38-03010 Rev. *A

Page 3 of 14

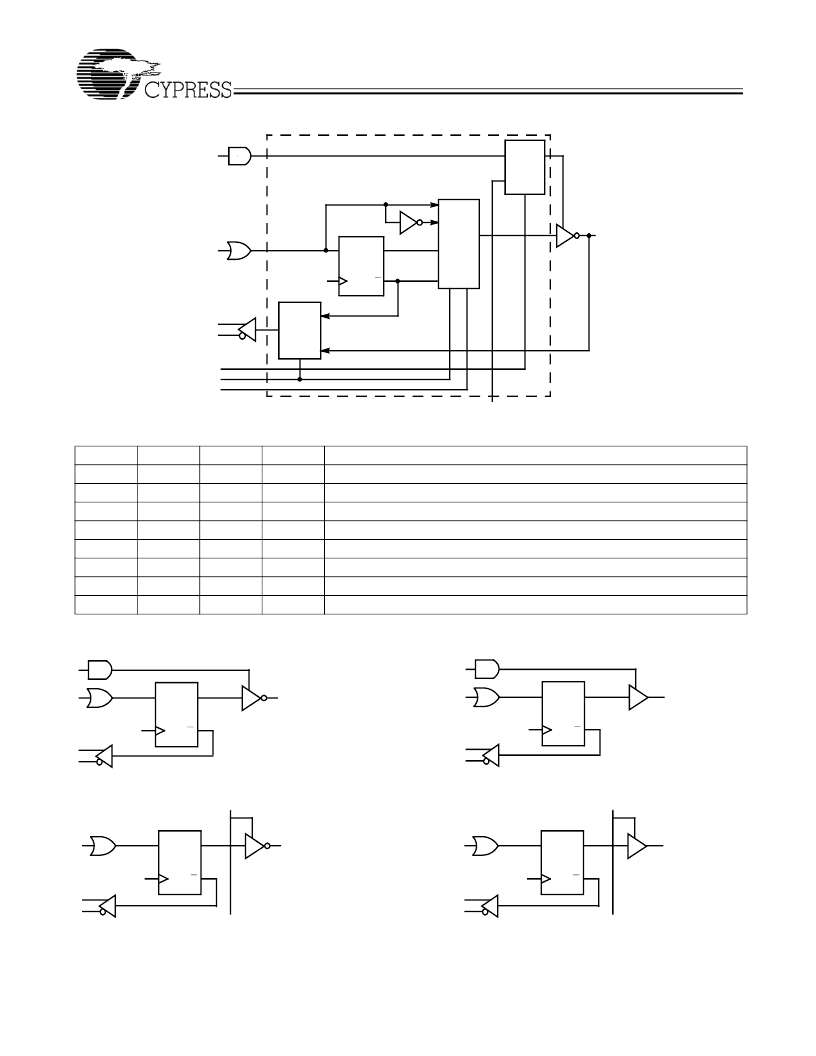

Programmable Output Cell

Configuration Table

Figure

1

2

5

6

3

4

7

8

C

2

0

0

0

0

1

1

1

1

C

1

0

0

1

1

0

0

1

1

C

0

0

1

0

1

0

1

0

1

Configuration

Product Term OE/Registered/Active LOW

Product Term OE/Registered/Active HIGH

Product Term OE/Combinatorial/Active LOW

Product Term OE/Combinatorial/Active HIGH

Pin 13 OE/Registered/Active LOW

Pin 13 OE/Registered/Active HIGH

Pin 13 OE/Combinatorial/Active LOW

Pin 13 OE/Combinatorial/Active HIGH

OUTPUT

SELECT

MUX

C

1

C

0

Q

Q

D

CP

INPUT/

FEED–

BACK

MUX

C

3

C

1

C

0

01

00

11

10

0

1

C

2

OUTPUT

ENABLE

MUX

C

2

PIN 13

OE PRODUCTTERM

Registered Output Configurations

Figure 1. Product Term OE/Active LOW

Figure 2. Product Term OE/Active HIGH

Figure 3. Pin 13 OE/Active LOW

Figure 4. Pin 13 OE/Active HIGH

Q

Q

D

CP

C

2

= 0

C

1

= 0

C

0

= 0

Q

Q

D

CP

C

2

= 0

C

1

= 0

C

0

= 1

Q

Q

D

CP

C

2

= 1

C

1

= 0

C

0

= 0

Q

Q

D

CP

C

2

= 1

C

1

= 0

C

0

= 1

相關PDF資料 |

PDF描述 |

|---|---|

| PLDC20RA10 | Reprogrammable Asynchronous CMOS Logic Device(重復編程異步CMOS邏輯器件) |

| PLF8577C | LCD direct/duplex driver with I2C-bus interface |

| PLL0930A | PHASE LOCKED LOOP |

| PLL1000A | PHASE LOCKED LOOP |

| PLL103-02 | DDR SDRAM Buffer for Desktop PCs with 4 DDR DIMMS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PLDC20G10B-15HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

| PLDC20G10B-15JC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

| PLDC20G10B-15JI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

| PLDC20G10B-15PC | 制造商:Cypress Semiconductor 功能描述:SPLD PLDC20G10B Family 10 Macro Cells 62.5MHz CMOS Technology 5V 24-Pin PDIP 制造商:Cypress Semiconductor 功能描述:SPLD PLDC20G10B Family 10 Macro Cells 62.5MHz 5V 24-Pin PDIP |

| PLDC20G10B-15PI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:UV-Erasable/OTP PLD |

發(fā)布緊急采購,3分鐘左右您將得到回復。