- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378205 > RTL8139L (Electronic Theatre Controls, Inc.) REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT PDF資料下載

參數(shù)資料

| 型號: | RTL8139L |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| 中文描述: | 瑞昱3.3V的單芯片快速以太網(wǎng)控制器電源管理 |

| 文件頁數(shù): | 41/62頁 |

| 文件大?。?/td> | 648K |

| 代理商: | RTL8139L |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

RTL8139C(L)

2002/01/10

Rev.1.4

41

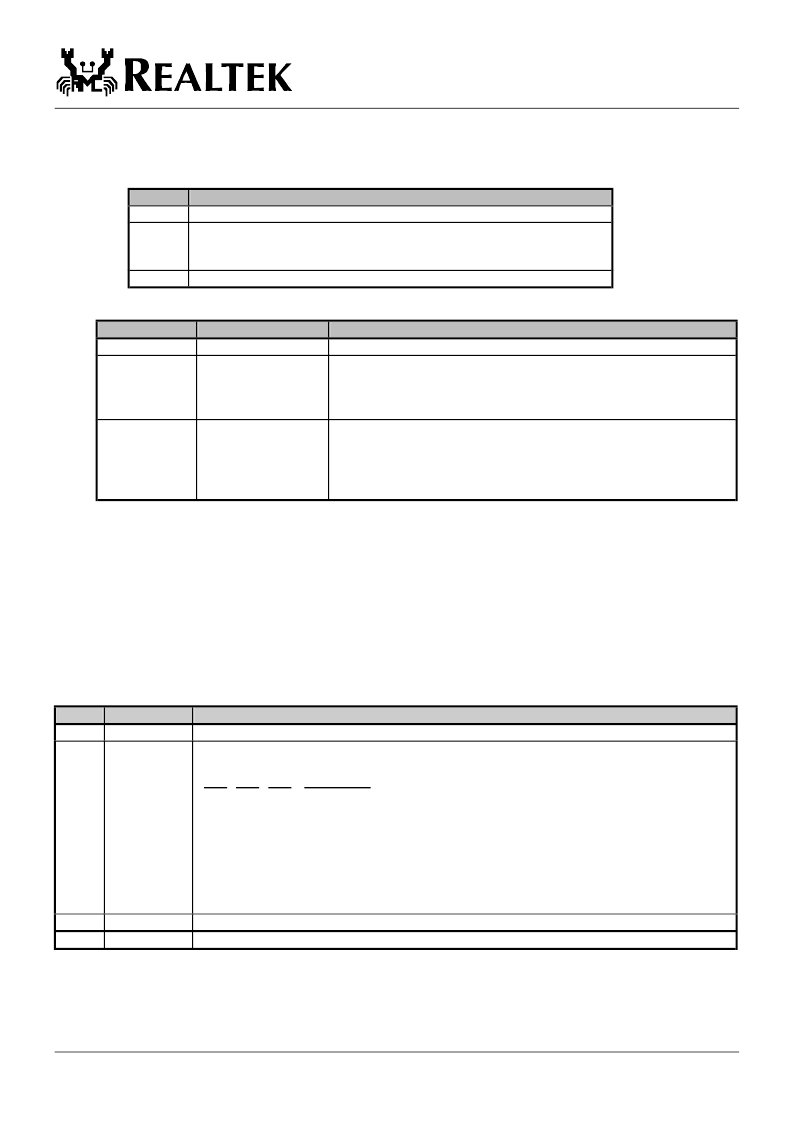

CISPtr:

CardBus CIS Pointer. This field is valid only when CardB_En (bit3, Config3) = 1. The value of this register is

auto-loaded from 93C46 or 93C56 (from offset 30h-31h).

-

Bit 2-0: Address Space Indicator

Bit2-0

0

Not supported. (CIS begins in device-dependent configuration space.)

1-6

The CIS begins in the memory address governed by one of the six Base

Address Registers. Ex., if the value is 2, then the CIS begins in the memory

address space governed by Base Address Register 2.

7

The CIS begins in the Expansion ROM space.

Bit27-3: Address Space Offset

Bit31-28: ROM Image number

Bit2-0

Space Type

Address Space Offset Values

0

Configuration space

Not supported.

X; 1

≤

X

≤

6

Memory space

0h

≤

value

≤

FFFF FFF8h. This is the offset into the memory address space

governed by Base Address Register X. Adding this value to the value in the

Base Address Register gives the location of the start of the CIS. For

RTL8139C(L), the value is 100h.

7

Expansion ROM

0

≤

image number

≤

Fh, 0h

≤

value

≤

0FFF FFF8h. This is the offset into the

expansion ROM address space governed by the Expansion ROM Base

Register. The image number is in the uppermost nibble of the CISPtr

register. The value consists of the remaining bytes. For RTL8139C(L), the

image number is 0h.

This read-only register points to where the CIS begins, in one of the following spaces:

i.

Memory space --- The CIS may be in any of the memory spaces from offset 100h and up after being

auto-loaded from 93C56. The CIS is stored in 93C56 EEPROM physically from offset 80h-FFh.

ii.

Expansion ROM space --- The CIS is stored in expansion ROM physically within the 128KB max.

Meaning

-

-

SVID:

Subsystem Vendor ID. This field will be set to a value corresponding to the PCI Subsystem Vendor ID in the external

EEPROM. If there is no EEPROM, this field will default to a value of 11ECh which is Realtek Semiconductor's PCI

Subsystem Vendor ID.

SMID:

Subsystem ID. This field will be set to a value corresponding to the PCI Subsystem ID in the external EEPROM. If there

BMAR:

This register specifies the base memory address for memory accesses to the RTL8139C(L) operational registers. This

register must be initialized prior to accessing any of the RTL8139C(L)'s registers with memory access.

Bit

31-18

17-11

Symbol

BMAR31-18 Boot ROM Base Address

ROMSIZE

These bits indicate how many Boot ROM spaces to be supported.

The Relationship between Config 0 <BS2:0> and BMAR17-11 is the following:

BS2 BS1 BS0 Description

0

0

0

No Boot ROM, BROMEN=0 (R)

0

0

1

8K Boot ROM, BROMEN (R/W), BMAR12-11 = 0 (R), BMAR17-13 (R/W)

0

1

0

16K Boot ROM, BROMEN (R/W), BMAR13-11 = 0 (R), BMAR17-14 (R/W)

0

1

1

32K Boot ROM, BROMEN (R/W), BMAR14-11 = 0 (R), BMAR17-15 (R/W)

1

0

0

64K Boot ROM, BROMEN (R/W), BMAR15-11 = 0 (R), BMAR17-16 (R/W)

1

0

1

128K Boot ROM, BROMEN(R/W), BMAR16-11=0 (R), BMAR17 (R/W)

1

1

0

unused

1

1

1

unused

-

Reserved (read back 0)

BROMEN

Boot ROM Enable: This is used by the PCI BIOS to enable accesses to Boot ROM.

Description

10-1

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8139 | REALTEK 3.3V SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139A | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139B | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8139D | REALTEK SINGLE CHIP FAST ETHERNET CONTROLLER WITH POWER MANAGEMENT |

| RTL8201 | REALTEK SINGLE CHIP SINGLE PORT 10/100M FAST ETHERNET PHYCEIVER RTL8201BL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8150 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8150L(M) Specifications |

| RTL8168 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:INTEGRATED GIGABIT ETHERNET CONTROLLER FOR PCI EXPRESS TM |

| RTL8169 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RTL8169 Specification |

| RTL8181 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Wireless LAN Access Point/Gateway Controller |

| RTL8187L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Wireless LAN network interface controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。