- 您現(xiàn)在的位置:買賣IC網 > PDF目錄373330 > RTL8305SB RTL8305SB PDF資料下載

參數(shù)資料

| 型號: | RTL8305SB |

| 英文描述: | RTL8305SB |

| 中文描述: | RTL8305SB |

| 文件頁數(shù): | 21/66頁 |

| 文件大小: | 963K |

| 代理商: | RTL8305SB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

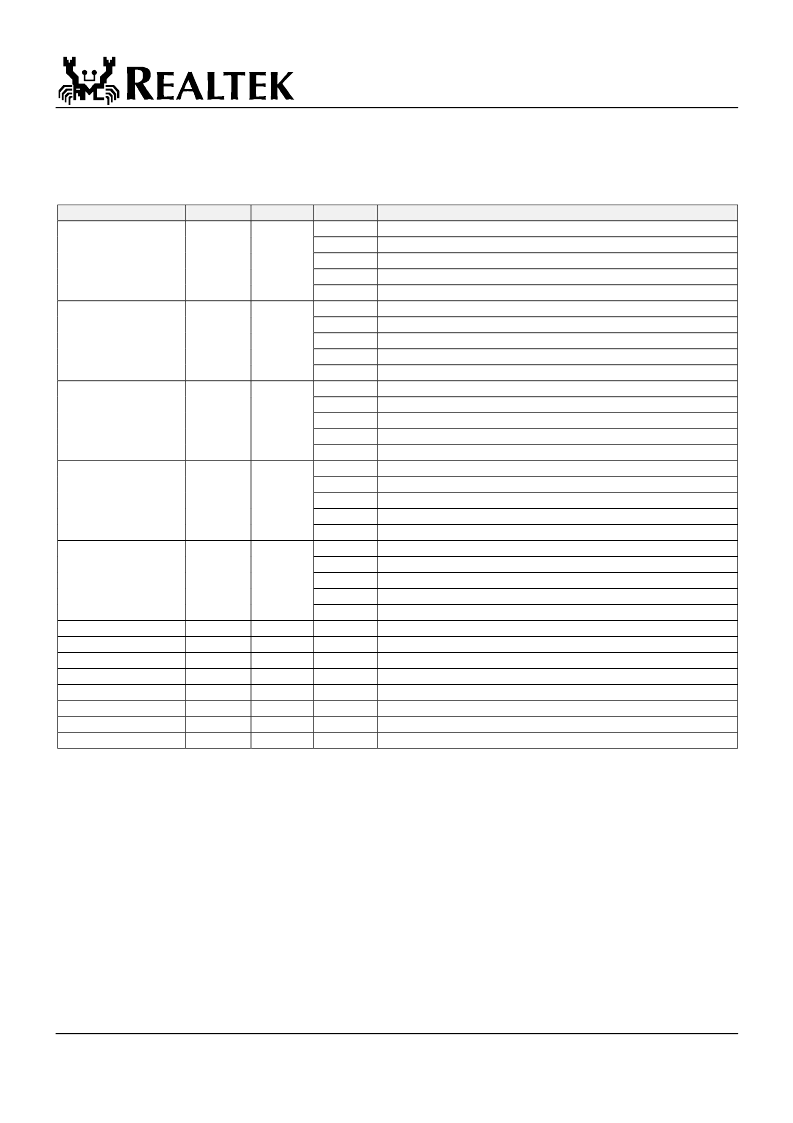

6. Register Description

RTL8305SB

2002/04/09

21

Rev.1.0

Hardware Reset: pin RESET# = 0 to 1. Reset all then load EEPROM and Pin registers with serial EEPROM and Pins strappings.

Soft Reset: Write bit15 of Reg16 of PHY3 as 1. Reset all except loading EEPROM and Pin Registers with serial EEPROM and Pins.

After updating the EEPROM or Pin registers via SMI, the external device has to do soft reset in order to change the configuration.

Name

Soft Reset

PHY

Register

0

Control Register

1

Status Register

4

Auto-Negotiation Advertisement Register

5

Auto-Negotiation Link Partner Ability Register

6

Auto-Negotiation Expansion Registers

0

Control Register

1

Status Register

4

Auto-Negotiation Advertisement Register

5

Auto-Negotiation Link Partner Ability Register

6

Auto-Negotiation Expansion Registers

0

Control Register

1

Status Register

4

Auto-Negotiation Advertisement Register

5

Auto-Negotiation Link Partner Ability Register

6

Auto-Negotiation Expansion Registers

0

Control Register

1

Status Register

4

Auto-Negotiation Advertisement Register

5

Auto-Negotiation Link Partner Ability Register

6

Auto-Negotiation Expansion Registers

0

Control Register

1

Status Register

4

Auto-Negotiation Advertisement Register

5

Auto-Negotiation Link Partner Ability Register

6

Auto-Negotiation Expansion Registers

EEPROM Reg0

Need

0

16~22

Register for EEPROM

EEPROM Reg1

Need

1

16~31

Register for EEPROM

Pin Reg

Need

2

16

Register for some Pins

Pin & EEPROM Reg

Need

2

17

Register for some Pins and EEPROM

Port Control Reg

No

3

16

Register for Port Control

EEPROM Reg

Need

3

17~20

Register for EEPROM

RO: Read Only

RW: Read/Write

LL: Latch Low until clear

LH: Latch High until clear

SC: Self Clearing

Register Description

Port0 PHY Reg

No

0

Port1 PHY Reg

No

1

Port2 PHY Reg

No

2

Port3 PHY Reg

No

3

Port4 PHY Reg

No

4

相關PDF資料 |

PDF描述 |

|---|---|

| RTL8316 | Specifications |

| RTL8801 | Specifications |

| RTM5070 | IR LEUCHTELEMENT ZUR FRONTPLATTENMONTAGE |

| RTP-PT100 | MESSFUEHLER PT100 EXTERN |

| RTR25 | "CLOCK 8""RIGHTIME - RADIO CONTROL" |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8305SC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:用于100M網絡交換 |

| RTL8305SC-LF | 制造商:Realtek Semiconductor 功能描述: |

| RTL8308B | 制造商:Realtek Semiconductor 功能描述:8-PORT 10/100 ETHERNET SWITCH CONTROLLER WITH EMBEDDED MEMORY, PQFP128 |

| RTL8309SB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SINGLE-CHIP 9-PORT 10/100MBPS SWITCH CONTROLLER |

| RTL8309SB-LF | 制造商:Realtek Semiconductor 功能描述:RTL8309 Series 9 Port 10/100 Mbps Ethernet Switch Controller - PQFP-128 制造商:Realtek 功能描述:RTL8309 Series 9 Port 10/100 Mbps Ethernet Switch Controller - PQFP-128 |

發(fā)布緊急采購,3分鐘左右您將得到回復。