- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372112 > SAA7108E (NXP SEMICONDUCTORS) PC-CODEC PDF資料下載

參數(shù)資料

| 型號: | SAA7108E |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | PC-CODEC |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA156 |

| 封裝: | 15 X 15 MM, 1.15 MM HEIGHT, PLASTIC, SOT-472-1, BGA-156 |

| 文件頁數(shù): | 62/202頁 |

| 文件大小: | 983K |

| 代理商: | SAA7108E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁

2004 Mar 16

62

Philips Semiconductors

Product specification

PC-CODEC

SAA7108E; SAA7109E

9.1.4

S

YNCHRONIZATION

The prefiltered luminance signal is fed to the

synchronization stage. Its bandwidth is further reduced to

1 MHz by a low-pass filter. The sync pulses are sliced and

fed to the phase detectors where they are compared with

the sub-divided clock frequency. The resulting output

signal is applied to the loop filter to accumulate all phase

deviations. Internal signals (e.g. HCL and HSY) are

generated in accordance with analog front-end

requirements. The loop filter signal drives an oscillator to

generate the line frequency control signal (LFCO);

see Fig.27.

The detection of ‘pseudo syncs’ as part of the macrovision

copy protection standard is also done within the

synchronization circuit.

The result is reported as flag COPRO within the decoder

status byte at subaddress 1FH.

9.1.5

C

LOCK GENERATION CIRCUIT

The internal CGC generates all clock signals required for

the video input processor.

The internal signal LFCO is a digital-to-analog converted

signal provided by the horizontal PLL. It is a multiple of the

line frequency:

6.75 MHz = 429

×

f

H

(50 Hz), or

6.75 MHz = 432

×

f

H

(60 Hz).

The LFCO signal is multiplied Internally by a factor of

2 and 4 in the PLL circuit (including phase detector, loop

filtering, VCO and frequency divider) to obtain the output

clock signals. The rectangular output clocks have a 50%

duty cycle.

Table 32

Decoder clock frequencies

CLOCK

FREQUENCY (MHz)

XTAL

LLC

LLC2

LLC4 (internal)

LLC8 (virtual)

24.576 or 32.110

27

13.5

6.75

3.375

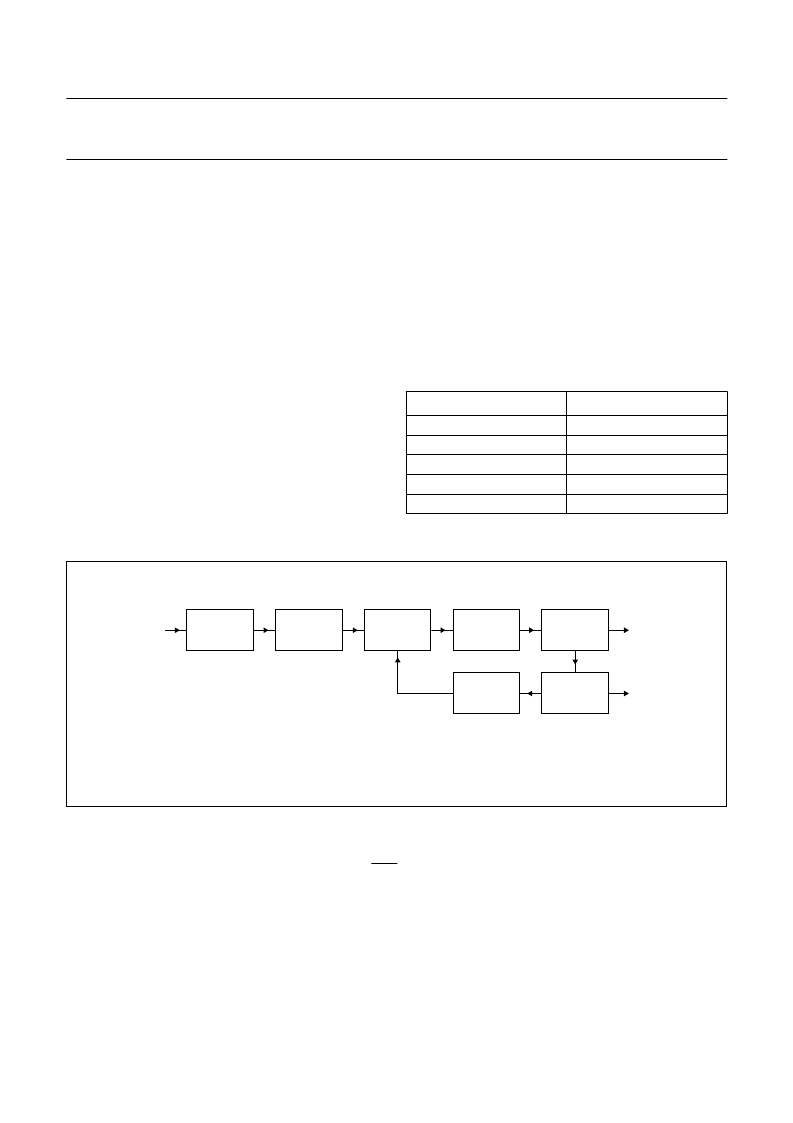

BAND PASS

FC = LLC/4

ZERO

CROSS

DETECTION

PHASE

DETECTION

LOOP

FILTER

DIVIDER

1/2

DIVIDER

1/2

OSCILLATOR

MHB330

LLC2

LLC

LFCO

Fig.27 Block diagram of the clock generation circuit.

9.1.6

P

OWER

-

ON RESET AND

CE

INPUT

A missing clock, insufficient digital or analog V

DDAd

supply voltages (below 2.7 V) will start the reset sequence; all outputs

are forced to 3-state (see Fig.28). The indicator output RES is LOW for approximately 128 LLC after the internal reset

and can be applied to reset other circuits of the digital TV system.

It is possible to force a reset by pulling the Chip Enable (CE) to ground. After the rising edge of CE and sufficient power

supply voltage, the outputs LLC, LLC2 and SDAd return from 3-state to active, while the other signals have to be

activated via programming.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SAA7109E | PC-CODEC |

| SAA7108AE | HD-CODEC |

| SAA7109A | HD-CODEC |

| SAA7109AE | HD-CODEC |

| SAA7110A | Digital Multistandard Colour Decoder(數(shù)字多標(biāo)準(zhǔn)彩色譯碼器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SAA7109 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PC-CODEC |

| SAA7109A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:HD-CODEC |

| SAA7109AE | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:HD-CODEC |

| SAA7109AE/V1,518 | 功能描述:視頻 IC HD- VIDEO CODEC RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| SAA7109AE/V1,557 | 功能描述:視頻 IC HD- VIDEO CODEC RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。