- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3779 > SX1506I091TRT (Semtech)IC GPIO EXP I2C 16CH 28UTQFN PDF資料下載

參數(shù)資料

| 型號: | SX1506I091TRT |

| 廠商: | Semtech |

| 文件頁數(shù): | 13/31頁 |

| 文件大小: | 0K |

| 描述: | IC GPIO EXP I2C 16CH 28UTQFN |

| 標準包裝: | 1 |

| 接口: | I²C |

| 輸入/輸出數(shù): | 16 |

| 中斷輸出: | 是 |

| 頻率 - 時鐘: | 400kHz |

| 電源電壓: | 2.5 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-UFQFN 裸露焊盤 |

| 供應商設備封裝: | 28-QFN-UT(4x4) |

| 包裝: | 標準包裝 |

| 其它名稱: | SX1506I091DKR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

WIRELESS & SENSING

Rev 3 – 16

th May 2012

www.semtech.com

20

SX1504/SX1505/SX1506

4/8/16 Channel GPIO

Addr

Name

Default

Bits

Description

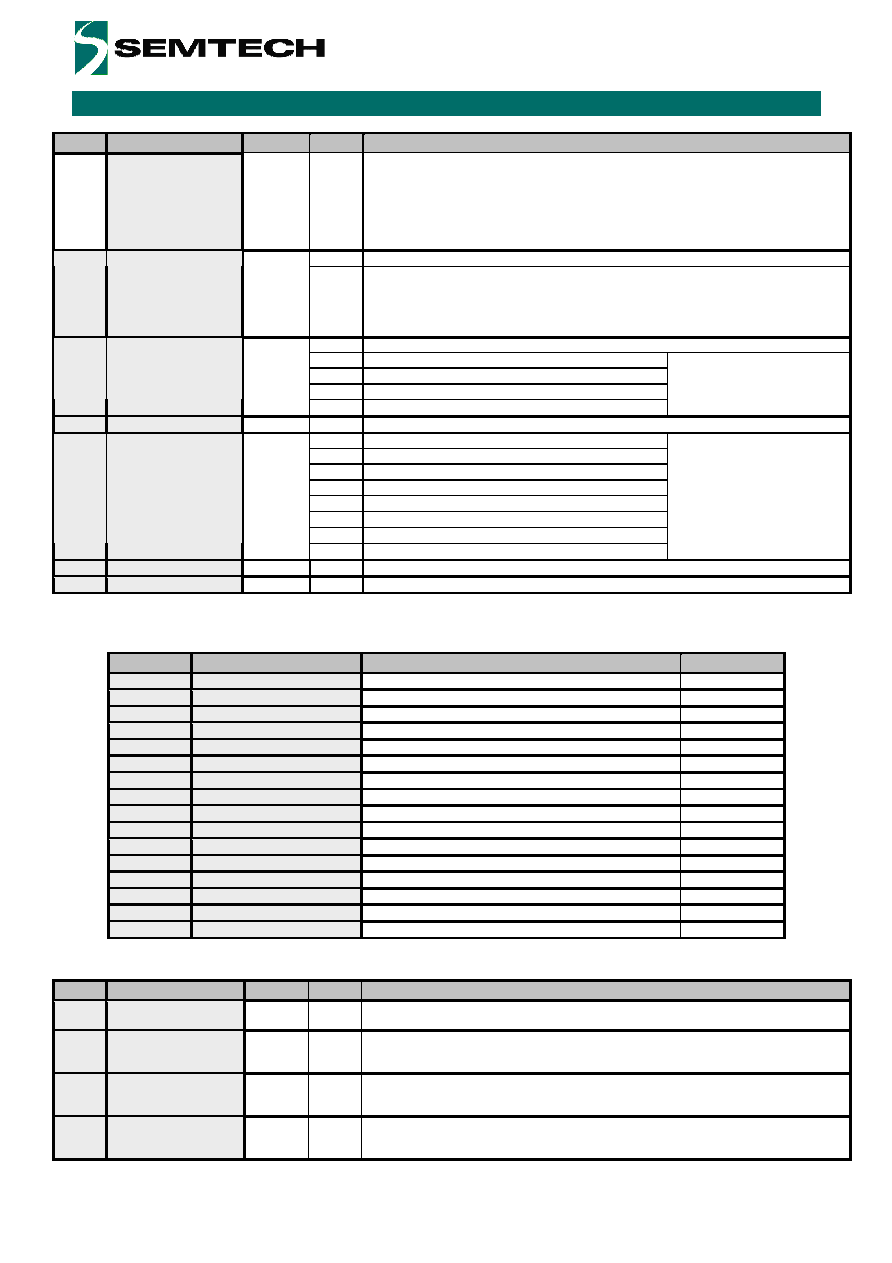

RegEventStatus

3:0

Event status of all IOs.

0 : No event has occured on this IO

1 : An event has occured on this IO (an edge as configured in relevant RegSense

register occured).

Writing '1' clears the bit in RegEventStatus and in RegInterruptSource if relevant.

If the edge sensitivity of the IO is changed, the bit(s) will be cleared automatically

7:2

Reserved. Must be set to 0 (default value)

0x10

RegPLDMode

0x00

1:0

PLDMode

00 : PLD disabled – Normal GPIO mode for I/O[3:0]

01 : PLD 2-to-1 mode – I/O[2] is a decode of I/O[1:0] as defined in RegPLDTable0

10 : PLD 3-to-1 mode – I/O[3] is a decode of I/O[2:0] as defined in RegPLDTable2

11 : Not used

7:4

Reserved. Must be set to 0 (default value)

3

Value to be output on I/O[2] when I/O[1:0] = 11

2

Value to be output on I/O[2] when I/O[1:0] = 10

1

Value to be output on I/O[2] when I/O[1:0] = 01

0x11

RegPLDTable0

0x00

0

Value to be output on I/O[2] when I/O[1:0] = 00

Applies only when PLDMode is

set to PLD 2-to-1 mode

0x12

RegPLDTable1

0xXX

7:0

Unused

7

Value to be output on I/O[3] when I/O[2:0] = 111

6

Value to be output on I/O[3] when I/O[2:0] = 110

5

Value to be output on I/O[3] when I/O[2:0] = 101

4

Value to be output on I/O[3] when I/O[2:0] = 100

3

Value to be output on I/O[3] when I/O[2:0] = 011

2

Value to be output on I/O[3] when I/O[2:0] = 010

1

Value to be output on I/O[3] when I/O[2:0] = 001

0x13

RegPLDTable2

0x00

0

Value to be output on I/O[3] when I/O[2:0] = 000

Applies only when PLDMode is

set to PLD 3-to-1 mode

0x14

RegPLDTable3

0xXX

7:0

Unused

0x15

RegPLDTable4

0xXX

7:0

Unused

Table 12 – SX1504 Configuration Registers Description

5.2

SX1505 8-channel GPIO

Address

Name

Description

Default

0x00

RegData

Data register

1111 1111

*

0x01

RegDir

Direction register

1111 1111

0x02

RegPullUp

Pull-up register

0000 0000

0x03

RegPullDown

Pull-down register

0000 0000

0x04

Reserved

Unused

XXXX XXXX

0x05

RegInterruptMask

Interrupt mask register

1111 1111

0x06

RegSenseHigh

Sense register for I/O[7:4]

0000 0000

0x07

RegSenseLow

Sense register for I/O[3:0]

0000 0000

0x08

RegInterruptSource

Interrupt source register

0000 0000

0x09

RegEventStatus

Event status register

0000 0000

0x10

RegPLDMode

PLD mode register

0000 0000

0x11

RegPLDTable0

PLD truth table 0

0000 0000

0x12

RegPLDTable1

PLD truth table 1

0000 0000

0x13

RegPLDTable2

PLD truth table 2

0000 0000

0x14

RegPLDTable3

PLD truth table 3

0000 0000

0x15

RegPLDTable4

PLD truth table 4

0000 0000

*Bits set as output take “1” as default value.

Table 13 – SX1505 Configuration Registers Overview

Addr

Name

Default

Bits

Description

0x00

RegData

0xFF

7:0

Write: Data to be output to the output-configured IOs

Read: Data seen at the IOs, independent of the direction configured.

0x01

RegDir

0xFF

7:0

Configures direction for each IO.

0 : IO is configured as an output

1 : IO is configured as an input

0x02

RegPullUp

0x00

7:0

Enables the pull-up for each IO

0 : Pull-up is disabled

1 : Pull-up is enabled

0x03

RegPullDown

0x00

7:0

Enables the pull-down for each IO

0 : Pull-down is disabled

1 : Pull-down is enabled

相關PDF資料 |

PDF描述 |

|---|---|

| 583718-3 | TW-LEAF CRP HSG 15 POS 100 C/L |

| 583861-5 | CONN HOUSING CARDEDGE 6DL POS |

| PCA9554ADB,112 | IC I/O EXPANDER I2C 8B 16SSOP |

| PCA9554ADB,118 | IC I/O EXPANDER I2C 8B 16SSOP |

| 583717-1 | CONN CARD EDGE 10 POS .100 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| SX1507_09 | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:Worlds Lowest Voltage Level |

| SX1507QB | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:World’s Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine |

| SX1507QBXXX | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:World’s Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine |

| SX1508B | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:Worlda??s Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine |

| SX1508BEVK | 制造商:Semtech Corporation 功能描述:EVAL KIT FOR SX1508 制造商:Semtech Corporation 功能描述:SX1507B/SX1508B EVALUATION KIT |

發(fā)布緊急采購,3分鐘左右您將得到回復。