- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄3779 > SX1506I091TRT (Semtech)IC GPIO EXP I2C 16CH 28UTQFN PDF資料下載

參數(shù)資料

| 型號: | SX1506I091TRT |

| 廠商: | Semtech |

| 文件頁數(shù): | 15/31頁 |

| 文件大小: | 0K |

| 描述: | IC GPIO EXP I2C 16CH 28UTQFN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 接口: | I²C |

| 輸入/輸出數(shù): | 16 |

| 中斷輸出: | 是 |

| 頻率 - 時(shí)鐘: | 400kHz |

| 電源電壓: | 2.5 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-UFQFN 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 28-QFN-UT(4x4) |

| 包裝: | 標(biāo)準(zhǔn)包裝 |

| 其它名稱: | SX1506I091DKR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

WIRELESS & SENSING

Rev 3 – 16

th May 2012

www.semtech.com

22

SX1504/SX1505/SX1506

4/8/16 Channel GPIO

Addr

Name

Default

Bits

Description

4

Value to be output on I/O[4] when I/O[2:0] = 100

3

Value to be output on I/O[4] when I/O[2:0] = 011

2

Value to be output on I/O[4] when I/O[2:0] = 010

1

Value to be output on I/O[4] when I/O[2:0] = 001

0

Value to be output on I/O[4] when I/O[2:0] = 000

7

Value to be output on I/O[3] when I/O[2:0] = 111

6

Value to be output on I/O[3] when I/O[2:0] = 110

5

Value to be output on I/O[3] when I/O[2:0] = 101

4

Value to be output on I/O[3] when I/O[2:0] = 100

3

Value to be output on I/O[3] when I/O[2:0] = 011

2

Value to be output on I/O[3] when I/O[2:0] = 010

1

Value to be output on I/O[3] when I/O[2:0] = 001

0x15

RegPLDTable4

0x00

0

Value to be output on I/O[3] when I/O[2:0] = 000

Applies only when

PLDModeLow is set to PLD 3-

to-2 mode

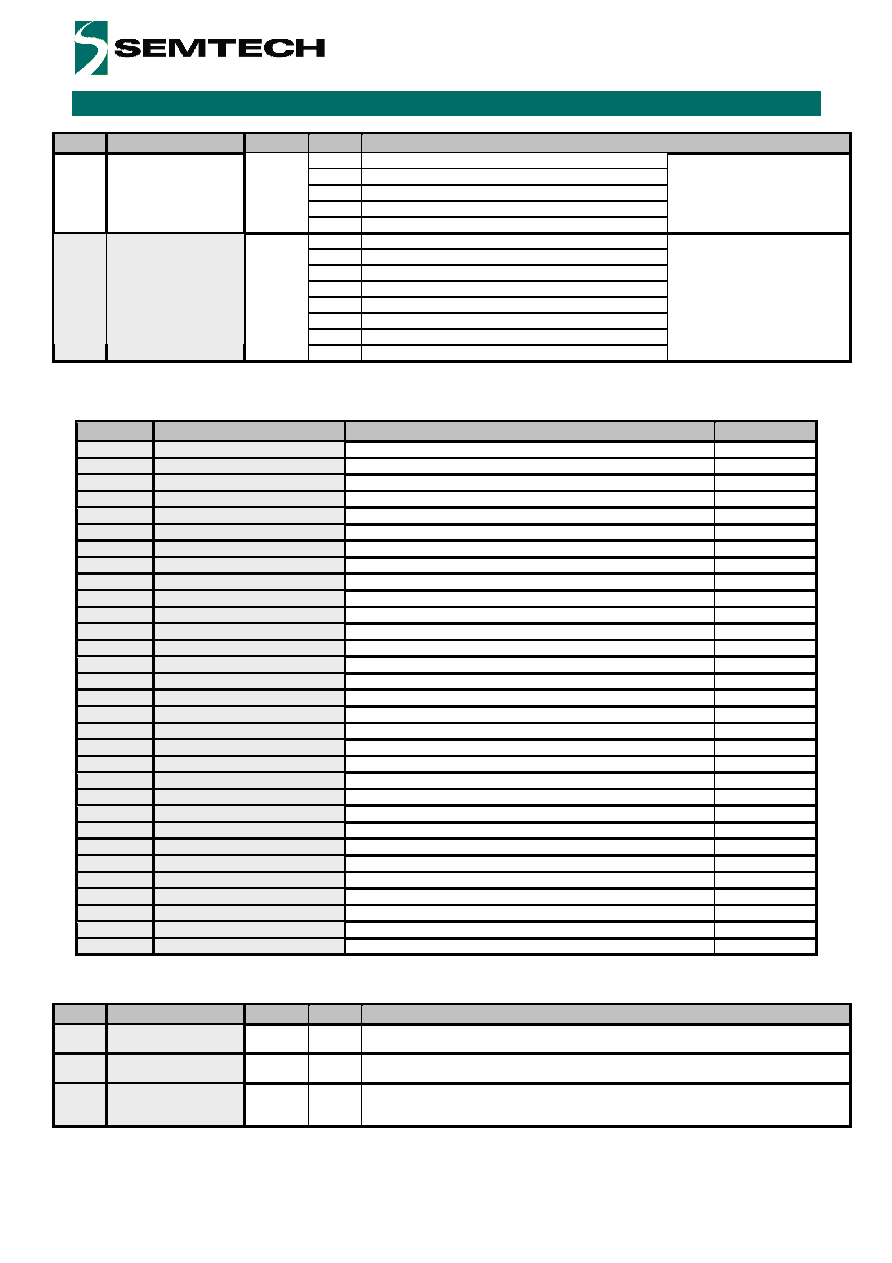

Table 14 – SX1505 Configuration Registers Description

5.3

SX1506 16-channel GPIO

Address

Name

Description

Default

0x00

RegDataB

Data register for Bank B I/O[15:8]

1111 1111

*

0x01

RegDataA

Data register for Bank A I/O[7:0]

1111 1111

*

0x02

RegDirB

Direction register for Bank B I/O[15:8]

1111 1111

0x03

RegDirA

Direction register for Bank A I/O[7:0]

1111 1111

0x04

RegPullUpB

Pull-up register for Bank B I/O[15:8]

0000 0000

0x05

RegPullUpA

Pull-up register for Bank A I/O[7:0]

0000 0000

0x06

RegPullDownB

Pull-down register for Bank B I/O[15:8]

0000 0000

0x07

RegPullDownA

Pull-down register for Bank A I/O[7:0]

0000 0000

0x08

RegInterruptMaskB

Interrupt mask register for Bank B I/O[15:8]

1111 1111

0x09

RegInterruptMaskA

Interrupt mask register for Bank A I/O[7:0]

1111 1111

0x0A

RegSenseHighB

Sense register for I/O[15:12]

0000 0000

0x0B

RegSenseHighA

Sense register for I/O[7:4]

0000 0000

0x0C

RegSenseLowB

Sense register for I/O[11:8]

0000 0000

0x0D

RegSenseLowA

Sense register for I/O[3:0]

0000 0000

0x0E

RegInterruptSourceB

Interrupt source register for Bank B I/O[15:8]

0000 0000

0x0F

RegInterruptSourceA

Interrupt source register for Bank A I/O[7:0]

0000 0000

0x10

RegEventStatusB

Event status register for Bank B I/O[15:8]

0000 0000

0x11

RegEventStatusA

Event status register for Bank A I/O[7:0]

0000 0000

0x20

RegPLDModeB

PLD mode register for Bank B I/O[15:8]

0000 0000

0x21

RegPLDModeA

PLD mode register for Bank A I/O[7:0]

0000 0000

0x22

RegPLDTable0B

PLD truth table 0 for Bank B I/O[15:8]

0000 0000

0x23

RegPLDTable0A

PLD truth table 0 for Bank A I/O[7:0]

0000 0000

0x24

RegPLDTable1B

PLD truth table 1 for Bank B I/O[15:8]

0000 0000

0x25

RegPLDTable1A

PLD truth table 1 for Bank A I/O[7:0]

0000 0000

0x26

RegPLDTable2B

PLD truth table 2 for Bank B I/O[15:8]

0000 0000

0x27

RegPLDTable2A

PLD truth table 2 for Bank A I/O[7:0]

0000 0000

0x28

RegPLDTable3B

PLD truth table 3 for Bank B I/O[15:8]

0000 0000

0x29

RegPLDTable3A

PLD truth table 3 for Bank A I/O[7:0]

0000 0000

0x2A

RegPLDTable4B

PLD truth table 4 for Bank B I/O[15:8]

0000 0000

0x2B

RegPLDTable4A

PLD truth table 4 for Bank A I/O[7:0]

0000 0000

0xAD

RegAdvanced

Advanced settings register

0000 0000

*Bits set as output take “1” as default value.

Table 15 – SX1506 Configuration Registers Overview

Addr

Name

Default

Bits

Description

0x00

RegDataB

0xFF

7:0

Write: Data to be output to the output-configured IOs

Read: Data seen at the IOs, independent of the direction configured.

0x01

RegDataA

0xFF

7:0

Write: Data to be output to the output-configured IOs

Read: Data seen at the IOs, independent of the direction configured.

0x02

RegDirB

0xFF

7:0

Configures direction for each IO.

0 : IO is configured as an output

1 : IO is configured as an input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 583718-3 | TW-LEAF CRP HSG 15 POS 100 C/L |

| 583861-5 | CONN HOUSING CARDEDGE 6DL POS |

| PCA9554ADB,112 | IC I/O EXPANDER I2C 8B 16SSOP |

| PCA9554ADB,118 | IC I/O EXPANDER I2C 8B 16SSOP |

| 583717-1 | CONN CARD EDGE 10 POS .100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SX1507_09 | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:Worlds Lowest Voltage Level |

| SX1507QB | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:World’s Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine |

| SX1507QBXXX | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:World’s Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine |

| SX1508B | 制造商:SEMTECH 制造商全稱:Semtech Corporation 功能描述:Worlda??s Lowest Voltage Level Shifting GPIO with LED Driver and Keypad Engine |

| SX1508BEVK | 制造商:Semtech Corporation 功能描述:EVAL KIT FOR SX1508 制造商:Semtech Corporation 功能描述:SX1507B/SX1508B EVALUATION KIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。