- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372405 > SZF2002 (NXP Semiconductors N.V.) Low voltage 8-bit microcontroller with 6-kbyte embedded RAM(帶6K字節(jié)嵌入RAM的低壓8位微控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | SZF2002 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Low voltage 8-bit microcontroller with 6-kbyte embedded RAM(帶6K字節(jié)嵌入RAM的低壓8位微控制器) |

| 中文描述: | 低電壓8位微控制器與6嵌入式RAM字節(jié)(帶6清音字節(jié)嵌入內(nèi)存的低壓8位微控制器) |

| 文件頁(yè)數(shù): | 30/76頁(yè) |

| 文件大小: | 431K |

| 代理商: | SZF2002 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)

1998 Aug 26

30

Philips Semiconductors

Product specification

Low voltage 8-bit microcontroller with

6-kbyte embedded RAM

SZF2002

16.1

Serial Control Register (S1CON)

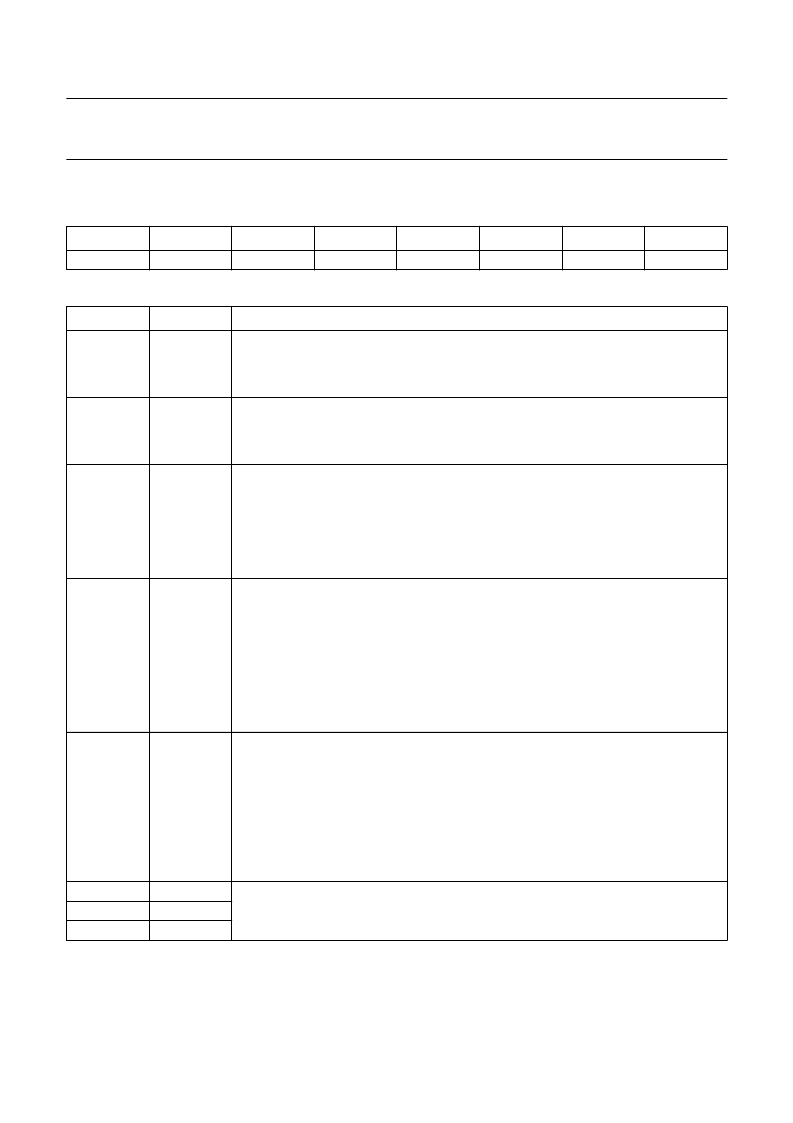

Table 23

Serial Control Register (SFR address D8H)

Table 24

Description of S1CON bits

7

6

5

4

3

2

1

0

CR2

ENS1

STA

STO

SI

AA

CR1

CR0

BIT

SYMBOL

DESCRIPTION

6

ENS1

Enable serial I/O.

When ENS1 = 0, the serial I/O is disabled. SDA and SCL outputs are

in the high-impedance state; P1.6 and P1.7 function as open-drain ports. When

ENS1 = 1, the serial I/O is enabled. Output port latches P1.6 and P1.7 must be set to

logic 1.

START flag.

When this bit is set in Slave mode, the SIO hardware checks the status of

the I

2

C-bus and generates a START condition if the bus is free or after the bus becomes

free. If STA is set while the SIO is in Master mode, SIO will generate a repeated START

condition.

STOP flag.

With this bit set while in Master mode a STOP condition is generated. When

a STOP condition is detected on the I

2

C-bus, the SIO hardware clears the STO flag.

STO may also be set in Slave mode in order to recover from an error condition. In this

case no STOP condition is transmitted to the I

2

C-bus. However, the SIO hardware

behaves as if a STOP condition has been received and releases the SDA and SCL

lines. The SIO then switches to the not addressed Slave receiver mode. The STOP flag

is cleared by the hardware.

SIO interrupt flag.

This flag is set and an interrupt is generated, after any of the

following events occur:

A START condition is generated in Master mode

Own slave address has been received during AA = 1

The general call address has been received while GC (S1ADR.0) = 1 and AA = 1

A data byte has been received or transmitted in Master mode (even if arbitration is lost)

A data byte has been received or transmitted as selected slave

A STOP or START condition is received as selected slave receiver or transmitter.

Assert Acknowledge.

When this bit is set, an acknowledge (LOW level to SDA) is

returned during the acknowledge clock pulse on the SCL line when:

Own slave address is received

General call address is received; GC (S1ADR.0) = 1

A data byte is received while the device is programmed to be a Master receiver

A data byte is received while the device is a selected Slave receiver.

When this bit is reset, no acknowledge is returned. Consequently, no interrupt is

requested when the own slave address or general call address is received.

Clock Rate selection.

These 3 bits determine the serial clock frequency when SIO is in

the Master mode. See Table 25.

5

STA

4

STO

3

SI

2

AA

7

1

0

CR2

CR1

CR0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SZF2002HL | Low voltage 8-bit microcontroller with 6-kbyte embedded RAM |

| T1012D | STANDARD TRIACS |

| T1012DH | STANDARD TRIACS |

| T1012M | STANDARD TRIACS |

| T1012MH | STANDARD TRIACS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SZF2002HL | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:Low voltage 8-bit microcontroller with 6-kbyte embedded RAM |

| SZF-41T-P0.7 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Disconnectable Crimp style Wire-to-wire connectors |

| SZFP6F0A | 制造商:SEOUL 制造商全稱(chēng):Seoul Semiconductor 功能描述:Z Power LED - Super high Flux output and high Luminance |

| SZG05A0A | 功能描述:大功率LED - 單色 Green 525nm 70lm 350mA RoHS:否 制造商:Cree, Inc. 照明顏色:Blue 波長(zhǎng):465 nm 光強(qiáng)度: 光通量/輻射通量:500 mW 正向電流:350 mA 正向電壓:3.1 V 安裝風(fēng)格:SMD/SMT 功率額定值: 系列:XB-D 封裝:Reel |

| SZG05A0A-1B | 制造商:Seoul Semiconductor 功能描述:Z5 Series Green LED 70lm Typical |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。