- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98285 > TPS65040ZQER (TEXAS INSTRUMENTS INC) 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 PDF資料下載

參數(shù)資料

| 型號: | TPS65040ZQER |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 |

| 封裝: | 5 X 5 MM, 0.50 MM PITCH, GREEN, PLASTIC, MICRO, BGA-71 |

| 文件頁數(shù): | 45/73頁 |

| 文件大小: | 1928K |

| 代理商: | TPS65040ZQER |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

www.ti.com

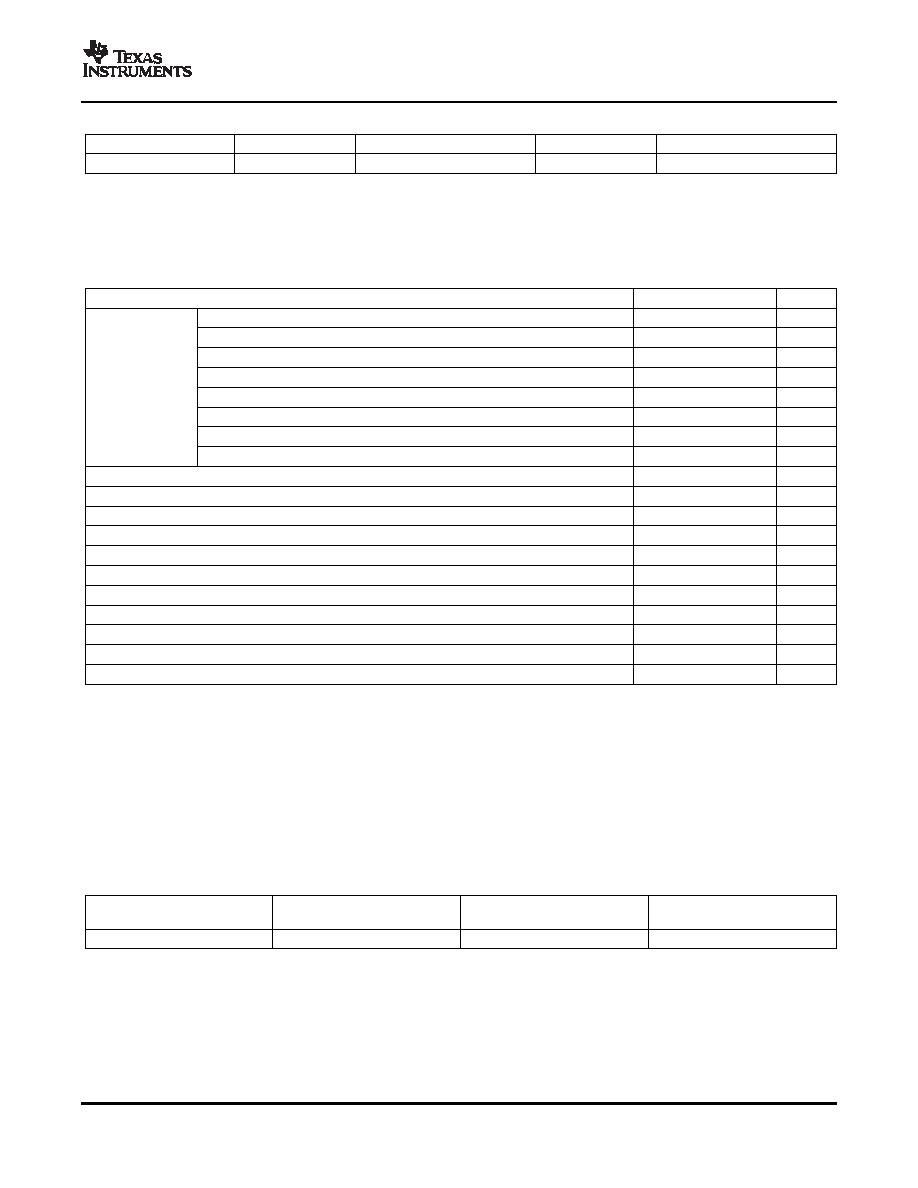

ABSOLUTE MAXIMUM RATINGS

DISSIPATION RATINGS

(1)

SLVS708B – NOVEMBER 2006 – REVISED APRIL 2007

ORDERING INFORMATION

PART NUMBER

TA

PACKAGE(1)

ORDERING

PACKAGE MARKING

TPS65040

–30

°C to 85°C

71-pin MicroStar Junior

TPS65040ZQE

PS65040

(1)

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

website at www.ti.com.

over operating free-air temperature range (unless otherwise noted) (1)

VALUE

UNIT

VIO1V8 pin with respect to GND2

–0.3 to 3.3

V

VBN1 pin with respect to GND1

–0.3 to 5.5

V

VBN2 pin with respect to GND2

–0.3 to 5.5

V

VBN3 pin with respect to GND3

–0.3 to 5.5

V

Supply voltage

VBN4 pin with respect to GND4

–0.3 to 5.5

V

VBN5 pin with respect to GND5

–0.3 to 5.5

V

VBDDP(2) pin with respect to DDGNDP(2)

–0.3 to 5.5

V

DDINA pin with respect to DDGNDA

–0.3 to 5.5

V

Input voltage range on REG_EN pin with respect to GND2

–0.3 to 5.5

V

Input voltage range on PABIAS1, PA_FB and ERR pins with respect to DDGNDA

–0.3 to 5.5

V

Input voltage range(2) on L1 and L2 pins with respect to DDGNDP

–0.3 to 5.5

V

Input voltage range on other pins(3)

–0.3 to 5.5

V

Input voltage range on SYSCLK_IN pin with respect to GND6

–0.3 to 3.3

V

Input voltage range on other input pins(4)

–0.3 to 3.3

V

Input voltage range on other pins(5)

–0.3 to 3.3

V

Peak LDO and SW output current(6)

Internally Limited

Peak current of power path(2) on VBDDP, L1, L2 pins with respect to DDGNDP

5

A

Storage temperature

–40 to 150

°C

Maximum junction temperature

125

°C

(1)

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

(2)

VBDDP is A4 and B4 pins, L1 is A5 and B5 pins, L2 is A7 and B7 pins, and DDGNDP is A6 and B6 pins.

(3)

Pin is VTCXO with respect to GND3. Pins are VGGE1_V28, VGGE2_V28, and VGGE3_V28 with respect to GND5. Pin is VOUT with

respect to DDGNDP. Pin is TEST with respect to DDGNDA.

(4)

Pins are CCLK, CDATA, CSTB, TSPCLK, TSPDIN, TSPEN, CRESET, WRFON, TXON, TXONFST, TBNDSEL1, TBNDSEL2,

SYSCLK_EN and SYSCLK_EN2 with respect to GND2.

(5)

Pins are AFC, PAVREF1, PAVREF2, and PAVREF3 with respect to GND1. Pins are SIN_SYSCLK1, SIN_SYSCLK2 and

SIN_SYSCLK3 with respect to GND6.

(6)

LDO and SW OUTPUT are V11_V28TX, PA_VDD, V12_V28RX, V_LNA_FEM, V15_V18A , V13_V28A, VTCXO, VGGE1_V28,

VGGE2_V28 and VGGE3_V28.

MAX POWER DISSIPATION

DERATING FACTOR

PACKAGE

RθJA

AT TA = 25°C

TA < 25°C

ZQE

51.23

°C/W

1.95 W

19.52 mW/

°C

(1)

Test board conditions

JEDEC High-K (2S2P) board used

3x3 inch, 4 layer

1 oz copper ground/power trace in the PCB

2 oz copper trace on the top/bottom of the PCB

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS650531IRGERQ1 | POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650532RGET | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650531RGER | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS65055RSMR | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

| TPS65058RGET | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS65050EVM-195 | 功能描述:電源管理IC開發(fā)工具 TPS65050-195 Eval Mod RoHS:否 制造商:Maxim Integrated 產(chǎn)品:Evaluation Kits 類型:Battery Management 工具用于評估:MAX17710GB 輸入電壓: 輸出電壓:1.8 V |

| TPS65050RSMR | 功能描述:PMIC 解決方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65050RSMRG4 | 功能描述:PMIC 解決方案 6Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65050RSMT | 功能描述:PMIC 解決方案 6-Channel Power Management IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65050RSMTG4 | 功能描述:PMIC 解決方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。