- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98285 > TPS65040ZQER (TEXAS INSTRUMENTS INC) 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 PDF資料下載

參數(shù)資料

| 型號: | TPS65040ZQER |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 8-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA71 |

| 封裝: | 5 X 5 MM, 0.50 MM PITCH, GREEN, PLASTIC, MICRO, BGA-71 |

| 文件頁數(shù): | 49/73頁 |

| 文件大小: | 1928K |

| 代理商: | TPS65040ZQER |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

V15_V18A

VGGE1_V28

SLVS708B – NOVEMBER 2006 – REVISED APRIL 2007

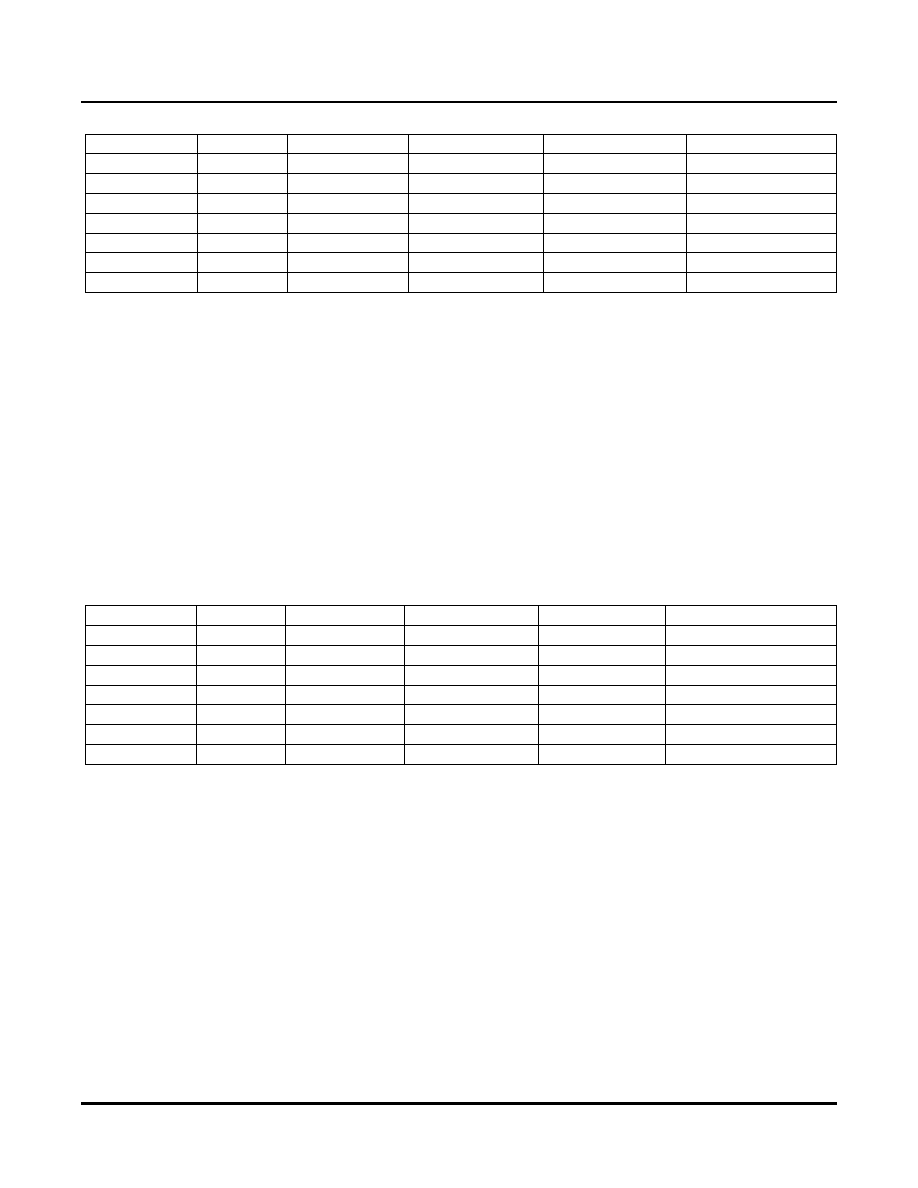

Table 7. V13_V28A ON/OFF and Normal Mode/Low Power Mode Control

REG_EN(1)

VIO1V8(1)

CRESET(1)

WRFON

r[PSCNT13]

V13_V28A

1

Normal Mode

1

0

1

Low Power Mode

1

0

OFF

1

0

OFF

0

Don't Care

OFF

1

0

Don't Care

OFF

1

0

Don't Care

1

Normal Mode

(1)

REG_EN, VIO1V8 and CRESET sequence is described in SEQUENCE CONTROL.

V15_V18A is an LDO that outputs 1.85 V, and is powered up during the power-up sequence of the TPS65040.

The SEQUENCE CONTROL Section provides more detail. Normal mode and low-power mode can be selected.

Normal mode provides high performance, and low-power mode provides low current consumption. The output

PMOS is stopped when the load current exceeds the limit value of the current-limit protection circuit in normal

mode; the power supply is shut down. When the load current falls below the limit values, current limit is

released. Current-limit protection is not available in the low-power mode. This LDO has a low-current mode and

a high-current mode in normal mode. The low-current mode and high-current mode correspond to light-load and

heavy-load conditions, respectively. The modes are changed automatically. This LDO on/off is controlled by

r[PSCNT15], and switches from normal mode to low-power mode with the WRFON pin. Register command

r[PSCNT15] can be controlled through the serial interface; default is 1. The SERIAL INTERFACE Section

provides greater detail. Note that the electrical characteristics of this LDO are not assured for the range of 2.7V

< VBAT < 3.1V function. When not used, turn it off or to the low-power mode. On/off control of V15_V18A and

switch control for normal mode/low-power mode are shown in Table 8.

Table 8. V15_V18A ON/OFF and Normal Mode/Low Power Mode Control

REG_EN(1)

VIO1V8(1)

CRESET(1)

WRFON

r[PSCNT15]

V15_V18A

1

Normal Mode

1

0

1

Low Power Mode

1

0

OFF

1

0

OFF

0

Don't Care

OFF

1

0

Don't Care

OFF

1

0

Don't Care

1

Normal Mode

(1)

REG_EN, VIO1V8 and CRESET sequence is described in SEQUENCE CONTROL.

VGGE1_V28 is an LDO that outputs 2.85 V, and is one of the LDOs enabled during the power-up sequence of

the TPS65040. More detail is given in the SEQUENCE CONTROL Section. The normal mode and low-power

mode can be selected, where normal mode provides high performance, and low-power mode provides low

current consumption. The output PMOS is stopped when the load current exceeds the limit value for the

current-limit protection circuit in normal mode, and the power supply is shut down. When the load current falls

below the limit value, current limit is released. Current-limit protection is not available in the low-power mode.

This LDO has a low-current mode and a high-current mode in normal mode. The low-current mode and

high-current mode correspond to light-load and heavy-load conditions, respectively. The modes are changed

automatically. LDO on/off is controlled by register command r[PSCNTGGE1]. Normal mode and low-power

mode are switched using register command r[GGE1psmode] at r[GGEmodecnt]=High, SYSCLK_EN2 pin at

r[GGEmodecnt]=Low. Register commands r[PSCNTGGE1], r[GGEmodecnt], and r[GGE1psmode] can be

controlled through the serial interface; the default is 1. More detail is provided in the SERIAL INTERFACE

Section. Note that the electrical characteristics for this LDO are not assured within the range of

3.0V<VBAT<3.1V function. Moreover, the output voltage also decreases by VBAT–VSAT, when VBAT

decreases. Turn off this LDO, or use the low-power mode, when in the VBAT<3 V condition. On/off control of

VGGE1_V28 and the switch control of normal mode/low-power mode are shown in Table 9.

53

相關PDF資料 |

PDF描述 |

|---|---|

| TPS650531IRGERQ1 | POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650532RGET | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS650531RGER | 5-CHANNEL POWER SUPPLY SUPPORT CKT, PQCC24 |

| TPS65055RSMR | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

| TPS65058RGET | 1.8 A DUAL SWITCHING CONTROLLER, 2475 kHz SWITCHING FREQ-MAX, PQCC32 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TPS65050EVM-195 | 功能描述:電源管理IC開發(fā)工具 TPS65050-195 Eval Mod RoHS:否 制造商:Maxim Integrated 產(chǎn)品:Evaluation Kits 類型:Battery Management 工具用于評估:MAX17710GB 輸入電壓: 輸出電壓:1.8 V |

| TPS65050RSMR | 功能描述:PMIC 解決方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65050RSMRG4 | 功能描述:PMIC 解決方案 6Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65050RSMT | 功能描述:PMIC 解決方案 6-Channel Power Management IC RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65050RSMTG4 | 功能描述:PMIC 解決方案 6-Ch Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。