- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄272329 > TS87C51RD2-VLMR (ATMEL CORP) 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | TS87C51RD2-VLMR |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP64 |

| 封裝: | 1.40 MM HEIGHT, VQFP-64 |

| 文件頁數(shù): | 77/83頁 |

| 文件大?。?/td> | 8336K |

| 代理商: | TS87C51RD2-VLMR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁第83頁

89

7707F–AVR–11/10

AT90USB82/162

Each half period of the external clock applied must be longer than one system clock cycle to

ensure correct sampling. The external clock must be guaranteed to have less than half the sys-

tem clock frequency (f

ExtClk < fclk_I/O/2) given a 50/50% duty cycle. Since the edge detector uses

sampling, the maximum frequency of an external clock it can detect is half the sampling fre-

quency (Nyquist sampling theorem). However, due to variation of the system clock frequency

and duty cycle caused by Oscillator source (crystal, resonator, and capacitors) tolerances, it is

recommended that maximum frequency of an external clock source is less than f

clk_I/O/2.5.

An external clock source can not be prescaled.

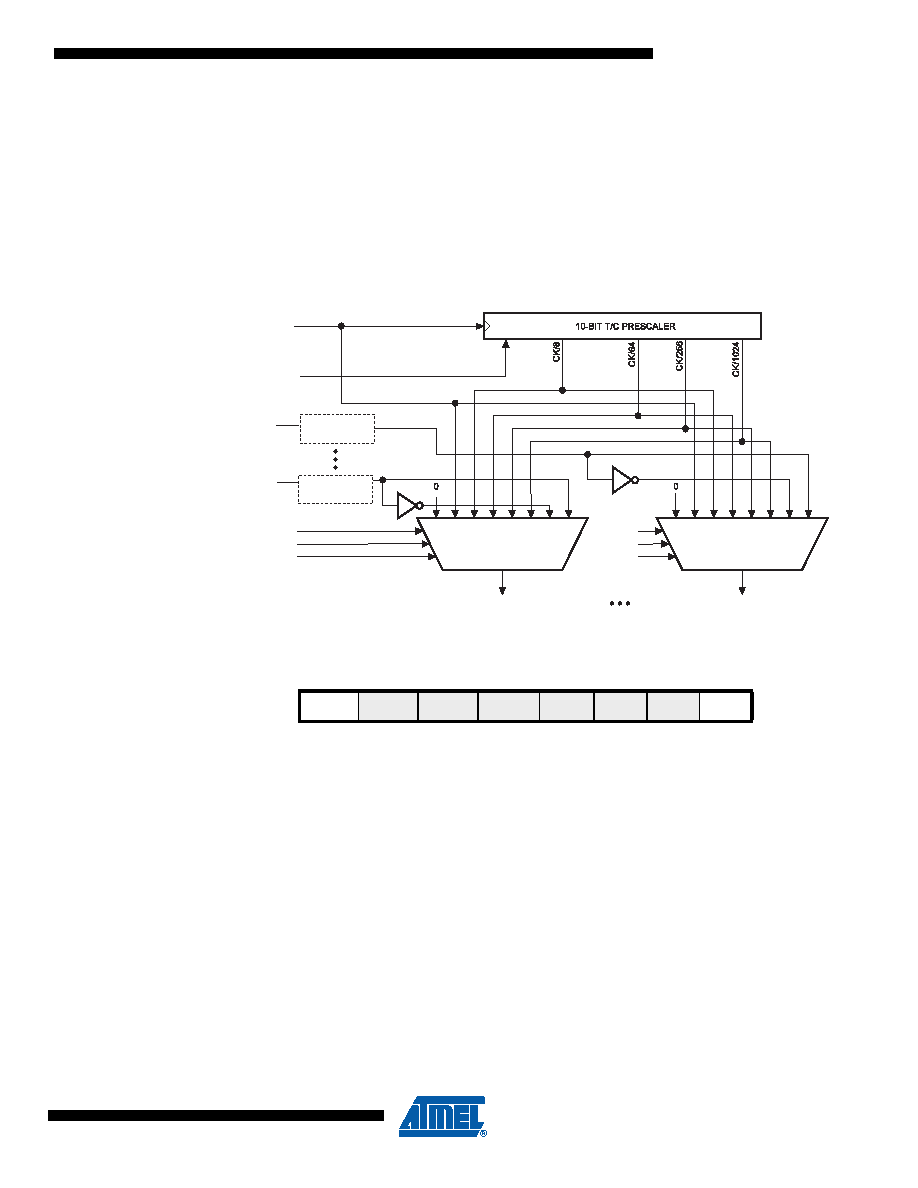

Figure 13-2. Prescaler for synchronous Timer/Counters

13.0.4

General Timer/Counter Control Register – GTCCR

Bit 7 – TSM: Timer/Counter Synchronization Mode

Writing the TSM bit to one activates the Timer/Counter Synchronization mode. In this mode, the

value that is written to the PSRASY and PSRSYNC bits is kept, hence keeping the correspond-

ing prescaler reset signals asserted. This ensures that the corresponding Timer/Counters are

halted and can be configured to the same value without the risk of one of them advancing during

configuration. When the TSM bit is written to zero, the PSRASY and PSRSYNC bits are cleared

by hardware, and the Timer/Counters start counting simultaneously.

Bit 0 – PSRSYNC: Prescaler Reset for Synchronous Timer/Counters

When this bit is one, Timer/Counter0 and Timer/Counter1, Timer/Counter3, Timer/Counter4 and

Timer/Counter5 prescaler will be Reset. This bit is normally cleared immediately by hardware,

except if the TSM bit is set. Note that Timer/Counter0 and Timer/Counter1 share the same pres-

caler and a reset of this prescaler will affect all timers.

PSR10

Clear

Tn

clk

I/O

Synchronization

TIMER/COUNTERn CLOCK SOURCE

clk

Tn

TIMER/COUNTERn CLOCK SOURCE

clk

Tn

CSn0

CSn1

CSn2

CSn0

CSn1

CSn2

Bit

7

6

5

4

3

2

1

0

TSM

–

-

PSRSY

NC

GTCCR

Read/Write

R/W

R

R/W

Initial Value

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS87C51RB2-VLEB | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP44 |

| TS80C52X2-LLCB | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 |

| TS80C51RA2-VLBB | 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 |

| TS87C52X2-VLEB | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP44 |

| TS87C54X2-VLBB | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS87C51U2 | 制造商:TEMIC 制造商全稱:TEMIC Semiconductors 功能描述:Double UART 8-bit CMOS Microcontroller, 0-60 MHz |

| TS87C51U2-EA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TS87C51U2-EB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TS87C51U2-EE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TS87C51U2-EJ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。