- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄2118 > TSB41AB3IPFPEP (Texas Instruments)IC 3PRT CABLE TXRX/ARBIT 80HTQFP PDF資料下載

參數(shù)資料

| 型號(hào): | TSB41AB3IPFPEP |

| 廠商: | Texas Instruments |

| 文件頁(yè)數(shù): | 9/55頁(yè) |

| 文件大小: | 0K |

| 描述: | IC 3PRT CABLE TXRX/ARBIT 80HTQFP |

| 標(biāo)準(zhǔn)包裝: | 96 |

| 類型: | 收發(fā)器 |

| 驅(qū)動(dòng)器/接收器數(shù): | 6/6 |

| 規(guī)程: | IEEE 1394 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 80-TQFP 裸露焊盤(pán) |

| 供應(yīng)商設(shè)備封裝: | 80-HTQFP(12x12) |

| 包裝: | 托盤(pán) |

| 產(chǎn)品目錄頁(yè)面: | 882 (CN2011-ZH PDF) |

| 其它名稱: | 296-22528 V62/03612-01XE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)

TSB41AB3EP

IEEE 1394a2000 THREEPORT CABLE TRANSCEIVER/ARBITER

SGLS122C JULY 2002 REVISED JUNE 2008

17

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

internal register configuration (continued)

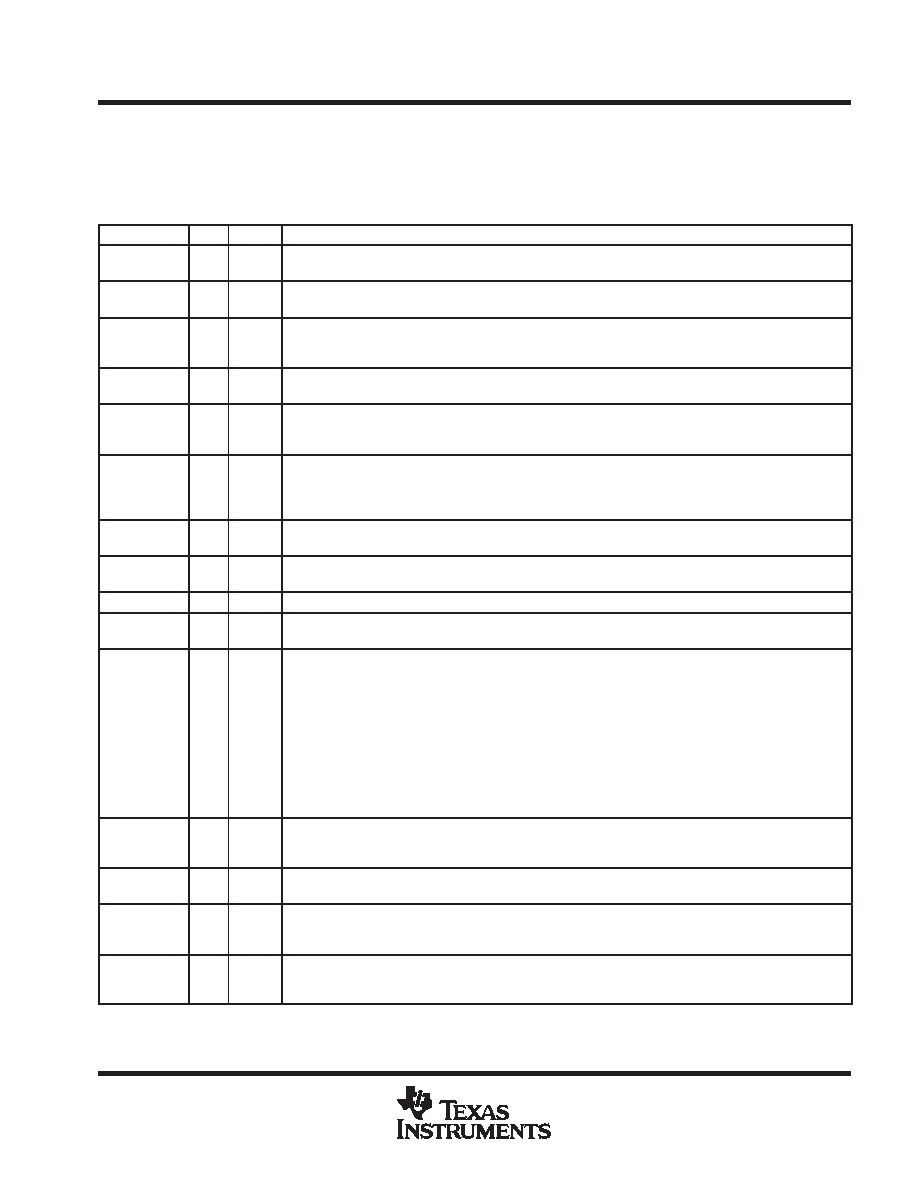

Table 2. Base Register Field Descriptions

FIELD

SIZE

TYPE

DESCRIPTION

Physical ID

6

Rd

This field contains the physical address ID of this node determined during self-ID. The physical-ID is invalid

after a bus reset until self-ID has completed as indicated by an unsolicited register-0 status transfer.

R

1

Rd

Root. This bit indicates that this node is the root node. The R bit is reset to 0 by bus reset, and is set to 1 during

tree-ID if this node becomes root.

CPS

1

Rd

Cable-power-status. This bit indicates the state of the CPS input terminal. The CPS terminal is normally tied to

serial bus cable power through a 400-k

resistor. A 0 in this bit indicates that the cable power voltage has

dropped below its threshold for ensured reliable operation.

RHB

1

Rd/Wr

Root-holdoff bit. This bit instructs the PHY to attempt to become root after the next bus reset. The RHB bit is

reset to 0 by a hardware reset is unaffected by a bus reset.

IBR

1

Rd/Wr

Initiate bus reset. This bit instructs the PHY to initiate a long (166

s) bus reset at the next opportunity. Any

receive or transmit operation in progress when this bit is set completes before the bus reset is initiated. The

IBR bit is reset to 0 after a hardware reset or a bus reset.

Gap_Count

6

Rd/Wr

Arbitration gap count. This value is used to set the subaction (fair) gap, arb-reset gap, and arb-delay times.

The gap count can be set either by a write to the register, or by reception or transmission of a PHY_CONFIG

packet. The gap count is reset to 3Fh by hardware reset or after two consecutive bus resets without an

intervening write to the gap count register (either by a write to the PHY register or by a PHY_CONFIG packet).

Extended

3

Rd

Extended register definition. For the TSB41AB3, this field is 111b, indicating that the extended register set is

implemented.

Num_Ports

4

Rd

Number of ports. This field indicates the number of ports implemented in the PHY. For the TSB41AB3 this field

is 3.

PHY_Speed

3

Rd

PHY speed capability. For the TSB41AB3 PHY this field is 010b, indicating S400 speed capability.

Delay

4

Rd

PHY repeater data delay. This field indicates the worst case repeater data delay of the PHY, expressed as

144+(delay

× 20) ns. For the TSB41AB3 this field is 0.

LCtrl

1

Rd/Wr

Link-active status control. This bit is used to control the active status of the LLC as indicated during self-ID.

The logical AND of this bit and the LPS active status is replicated in the L field (bit 9) of the self-ID packet. The

LLC is considered active only if both the LPS input is active and the LCtrl bit is set.

The LCtrl bit provides a software controllable means to indicate the LLC active status in lieu of using the LPS

input.

The LCtrl bit is set to 1 by hardware reset and is unaffected by bus-reset.

NOTE: The state of the PHY-LLC interface is controlled solely by the LPS input, regardless of the state of the

LCtrl bit. If the PHY-LLC interface is operational as determined by the LPS input being active, then received

packets and status information continues to be presented on the interface, and any requests indicated on the

LREQ input is processed, even if the LCtrl bit is cleared to 0.

C

1

Rd/Wr

Contender status. This bit indicates that this node is a contender for the bus or isochronous resource

manager. This bit is replicated in the c field (bit 20) of the self-ID packet. This bit is set to the state specified by

the C/LKON input terminal by a hardware reset and is unaffected by a bus reset.

Jitter

3

Rd

PHY repeater jitter. This field indicates the worst case difference between the fastest and slowest repeater

data delay, expressed as (jitter+1)

× 20 ns. For the TSB41AB3, this field is 0.

Pwr_Class

3

Rd/Wr

Node power class. This field indicates this node power consumption and source characteristics and is

replicated in the pwr field (bits 2123) of the self-ID packet. This field is reset to the state specified by the

PC0PC2 input terminals upon a hardware reset, and is unaffected by a bus reset. See Table 9.

RPIE

1

Rd/Wr

Resuming port interrupt enable. This bit, if set to 1, enables the port event interrupt (PIE) bit to be set

whenever resume operations begin on any port. This bit is reset to 0 by hardware reset and is unaffected by

bus reset.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP5150APBSRG4 | IC VIDEO DECODER 8BIT 32TQFP |

| TVP5154AIPNP | IC VIDEO DECODER 4CH 128-HTQFP |

| TW2804-FE | IC NTSC/PAL VIDEO DECOD 128PQF |

| TW2809-BC1-GR | IC INTERFACE |

| TW2815-TA1-GR | IC A/V CODEC/DECOD 4CH 100TQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB41AB3IPFPG4 | 制造商:Texas Instruments 功能描述:THREE PORT CBL TRNSCVR/ARBITER 1TX 1RX 400MBPS 80HTQFP - Rail/Tube |

| TSB41AB3MPFPEP | 功能描述:1394 接口集成電路 Enh Product 3Port Cable Xcvr/Arbiter RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB41AB3PFP | 功能描述:緩沖器和線路驅(qū)動(dòng)器 Three-Port Cable Xcvr/Arbiter RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| TSB41AB3PFPG4 | 功能描述:1394 接口集成電路 Three-Port Cable Xcvr/Arbiter RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB41BA3 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE1394B THREE PORT CABLE TRANSCEIVER/ARBITER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。