- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄365987 > TSPC106AVGSU83CE MEMORY CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | TSPC106AVGSU83CE |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內(nèi)存控制器 |

| 文件頁(yè)數(shù): | 16/40頁(yè) |

| 文件大小: | 569K |

| 代理商: | TSPC106AVGSU83CE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)

16

TSPC106

2102B

–

HIREL

–

02/02

PCI Interface Signals

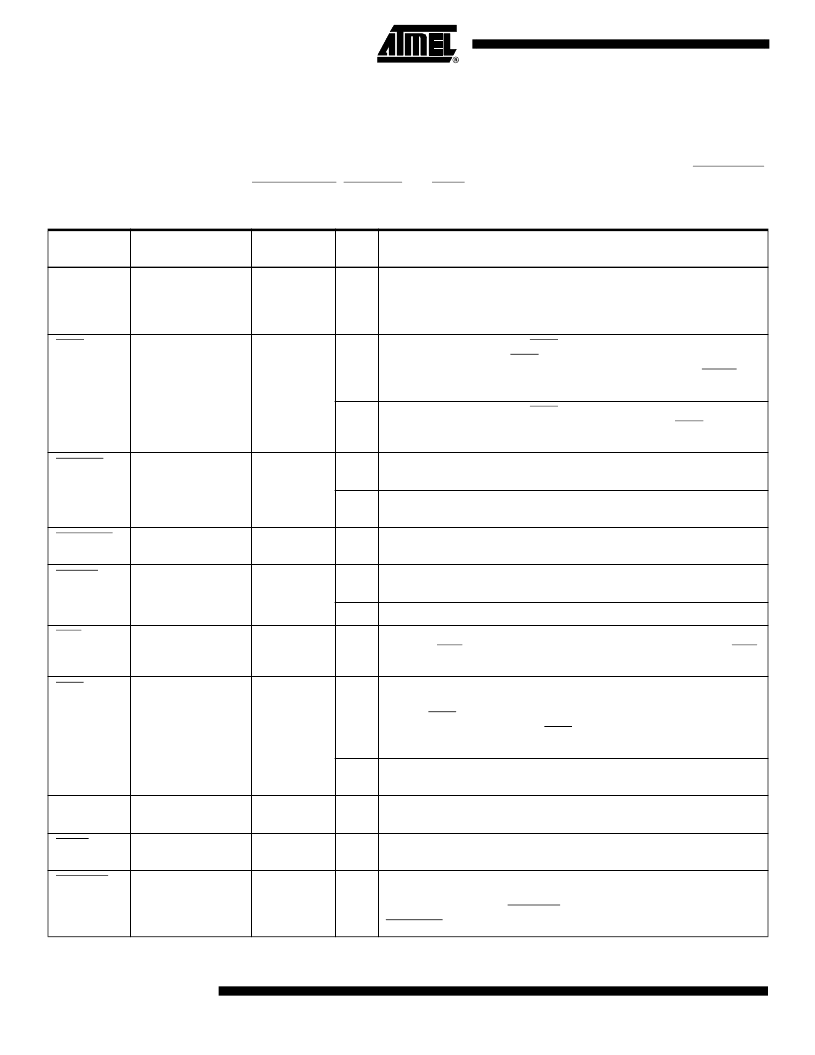

Table 7 lists the PCI interface signals and provides a brief description of their functions.

Note that the bits in Table 7 are referenced in little-endian format.

The PCI specification defines a sideband signal as any signal, not part of the PCI speci-

fication, that connects two or more PCI-compliant agent, and has meaning only to those

agents. The TSPC106 implements four PCI sideband signals -FLSHREQ,

ISA_MASTER, MEMACK and PIRQ.

Table 7.

PCI Interface Signals

Signal

Signal Name

Number of

Pins

I/O

Signal Description

AD[31:0]

Address/data

32

I/O

Represents the physical address during the address phase of a

transaction. During the data phase(s) of a PCI transaction, AD[31:0]

contain data. AD[7:0] define the least significant byte and AD[31:24]

the most significant byte.

C/BE[3:0]

Command/byte

enable

4

O

During the address phase, C/BE[3:0] define the PCI bus command.

During the data phase, C/BE[3:0] are used as byte enables. Byte

enables determine which byte lanes carry meaningful data. C/BE0

applies to the least significant byte.

I

During the address phase, C/BE[3:0] indicates the PCI bus command

that another master is sending. During the data phase C/BE[3:0]

indicate which byte lanes are valid.

DEVSEL

Device select

1

O

Indicates that the TSPC106 has decoded the address and is the target

of the current access.

I

Indicates that some PCI agent (other than the TSPC106) has decoded

its address as the target of the current access.

FLSHREQ

Flush request

1

I

Indicates that a device needs to have the TSPC106 flush all of its

current operations.

FRAME

Frame

1

O

Indicates that the TSPC106, acting as a PCI master, is initiating a bus

transaction.

I

Indicates that another PCI master is initiating a bus transaction.

GNT

PCI bus grant

1

I

Indicates that the TSPC106 has been granted control of the PCI bus.

Note that GNT is a point-to-point signal. Every master has its own GNT

SIGNAL.

IRDY

Initializer ready

1

O

Indicates that the TSPC106, acting as a PCI master, can complete the

current data phase of a PCI transaction. During a write, the TSPC106

asserts IRDY to indicate that valid data is present on AD[31:0]. During

a read, the TSPC106 asserts IRDY to indicate that it is prepared to

accept data.

I

Indicates another PCI master is able to complete the current data

phase of the transaction.

ISA_

MASTER

ISA master

1

I

Indicates that an ISA master is requesting system memory.

LOCK

Lock

1

I

Indicates that a master is requesting exclusive access to memory,

which may require multiple transactions to complete.

MEMACK

Memory

acknowledge

1

O

Indicates that the TSPC106 has flushed all of its current operations

and has blocked all 60x transfers except snoop copy-back operations.

The TSPC106 asserts MEMACK in response to assertion of

FLSHREQ after the flush is complete.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC106AVGSU83CG | MEMORY CONTROLLER |

| TSPC603RMG10LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMG12LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMG14LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMG6LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC106AVGSU83CG | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T66CE | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T66CG | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T83CE | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T83CG | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MEMORY CONTROLLER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。