- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365987 > TSPC106AVGSU83CE MEMORY CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | TSPC106AVGSU83CE |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內(nèi)存控制器 |

| 文件頁數(shù): | 21/40頁 |

| 文件大小: | 569K |

| 代理商: | TSPC106AVGSU83CE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

21

TSPC106

2102B

–

HIREL

–

02/02

After the C4 solder bump is reflowed, epoxy (encapsulant) is under-filled between the

die and the substrate. Under-fill material is commonly used on large high-power die;

however, this is not a requirement of the C4 technology. The package substrate is a

multilayer-co-fired ceramic. The package-to-board interconnection is via an array of

orthogonal 90/10 (lead/tin) solder balls on 1.27 mm pitch. During assembly of the

C4/CBGA package to the board, the high-melt balls do not collapse.

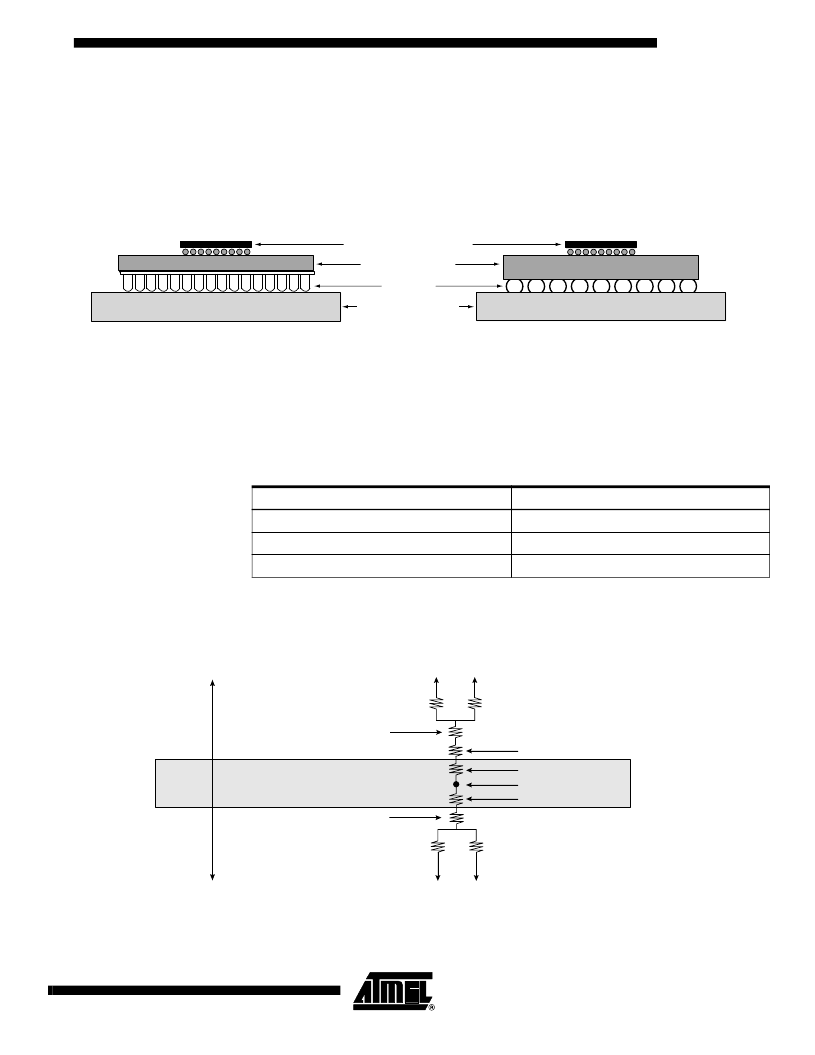

Figure 5.

Exploded Cross-section

Internal Package Conduction

Resistance

For the C4/CBGA packaging technology, the intrinsic conduction thermal resistance

paths are as follows:

the die junction-to-case thermal resistance

the die junction-to-lead thermal resistance

These parameters are shown in Table 12. In the C4/CBGA package, the silicon chip is

exposed; therefore, the package case is the top of the silicon.

Figure 6 shows a simplified thermal network in which a C4/CBGA package is mounted

on a printed-circuit board.

Figure 6.

C4/CBGA Package Mounted on a Printed Circuit Board

Note:

Internal package resistance differs from external package resistance.

CBGA Package

CI_CGA Package

Chip with C4 Encapsulant

Ceramic Substrate

BGA Joint

Printed Circuit Board

Table 12.

Thermal Resistance

Thermal Metric

Effective Thermal Resistance

Junction-to-case thermal resistance

0.133

°

C/W

Junction-to-lead (ball) thermal resistance

3.8

°

C/W (CBGA package)

Junction-to-lead (column) thermal resistance

4.0

°

C/W (CI_CGA package)

External Resistance

External Resistance

Internal Resistance

Radiation

Convection

Heat Sink

Thermal Interface Material

Die/Package

Die Junction

Package/Leads

Printed Circuit Board

Radiation

Convection

相關PDF資料 |

PDF描述 |

|---|---|

| TSPC106AVGSU83CG | MEMORY CONTROLLER |

| TSPC603RMG10LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMG12LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMG14LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

| TSPC603RMG6LC | MICROPROCESSOR|32-BIT|CMOS|BGA|255PIN|CERAMIC |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC106AVGSU83CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T66CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T66CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T83CE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

| TSPC106AVGU/T83CG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MEMORY CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復。