- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄365987 > TSPC106AVGU83CE MEMORY CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | TSPC106AVGU83CE |

| 英文描述: | MEMORY CONTROLLER |

| 中文描述: | 內(nèi)存控制器 |

| 文件頁數(shù): | 10/40頁 |

| 文件大?。?/td> | 569K |

| 代理商: | TSPC106AVGU83CE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

10

TSPC106

2102B

–

HIREL

–

02/02

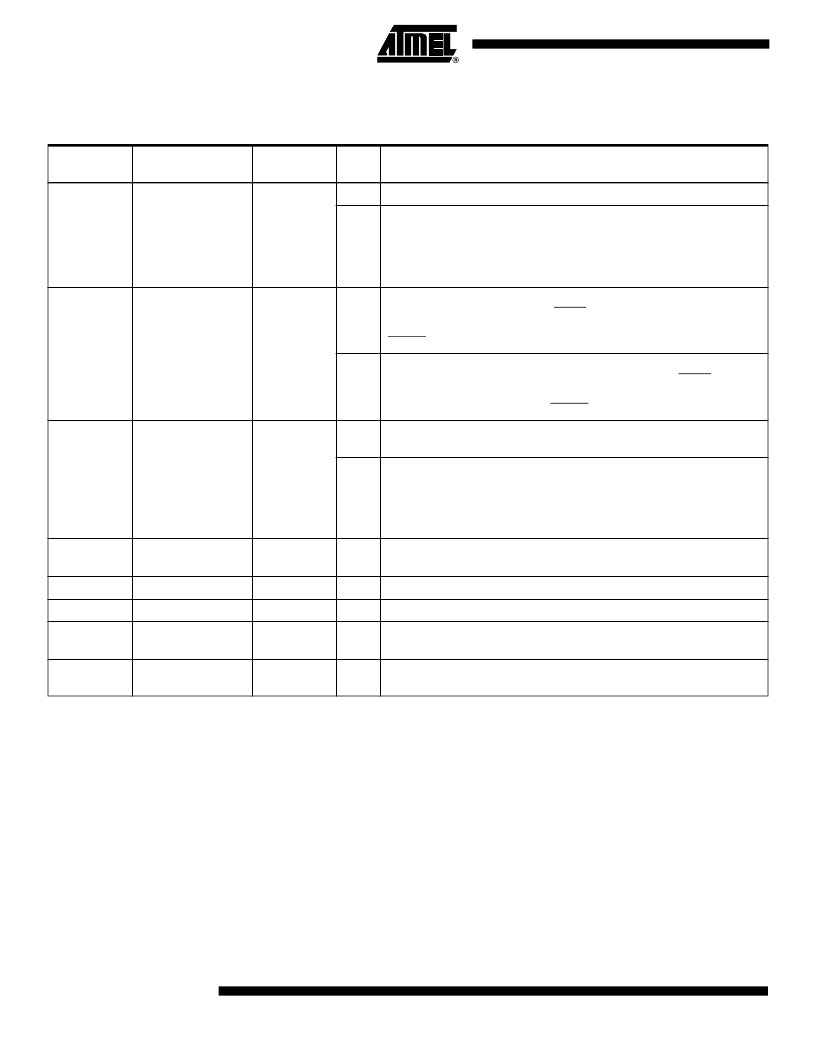

60x Processor Interface Signals

Table 2.

60x Processor Interface Signals

Signal

Signal Name

Number of

Pins

I/O

Signal Description

A[0:31]

Address bus

32

O

Specifies the physical address for 60x bus snooping.

I

Specifies the physical address of the bus transaction. For burst reads,

the address is aligned to the critical double-word address that missed

in the instruction or data cache. For burst writes, the address is aligned

to the double-word address of the cache line being pushed from the

data cache.

AACK

Address

acknowledge

1

O

Indicates that the address tenure of a transaction is terminated. On the

cycle following the assertion of AACK, the bus master releases the

address-tenure-related signals to a high impedance state and samples

ARTRY.

I

Indicates that an externally-controlled L2 cache is terminating the

address tenure. On the cycle following the assertion of AACK, the bus

master releases the address-tenure-related signals to a high

impedance state and samples ARTRY.

ARTRY

Address retry

1

O

Indicates that the initiating 60x bus master must retry the current

address tenure.

I

During a snoop operation, indicates that the 60x either requires the

current address tenure to be retried due to a pipeline collision or needs

to perform a snoop copy-back operation. During normal 60x bus cycles

in a multiprocessor system, indicates that the other 60x or external L2

controller requires the address tenure to be retried.

BG0

Bus grant 0

1

O

Indicates that the primary 60x may, with the proper qualification, begin

a bus transaction and assume mastership of the address bus.

BR0

Bus request 0

1

I

Indicates that the primary 60x requires the bus for a transaction.

CI

Cache inhibit

1

I/O

Indicates that an access is caching-inhibited.

DBG0

Data bus grant 0

1

O

Indicates that the 60x may, with the proper qualification, assume

mastership of the data bus.

DBGLB

Local bus slave

data bus grant

1

O

Indicates that the 60x processor is prepared to accept data and the

local bus slave should drive the data bus.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSPC106AVGU83CG | MEMORY CONTROLLER |

| TSPC106AMG66CE | MEMORY CONTROLLER |

| TSPC106AMG66CG | MEMORY CONTROLLER |

| TSPC106AMG83CE | MEMORY CONTROLLER |

| TSPC106AMG83CG | MEMORY CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSPC106AVGU83CG | 功能描述:IC PCI MEM CTRLR 83MHZ 303CBGA RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| TSPC120-124 | 制造商:Traco Power 功能描述:AC-DC CONV, DIN RAIL, 1 O/P, 120W, 5A, 24V; Power Supply Output Type:Adjustable, Fixed; Input Voltage VAC:85V to 132V, 187V to 264V; No. of Outputs:1; Output Voltage Nom.:24V; Output Current Max:5A; Output Power Max:120W ;RoHS Compliant: Yes 制造商:Traco Power 功能描述:DIN Rail PSU 24Vdc, 120W, 5A |

| TSPC240-124 | 制造商:Traco Power 功能描述:AC-DC CONV, DIN RAIL, 1 O/P, 240W, 10A, 24V; Power Supply Output Type:Adjustable, Fixed; Input Voltage VAC:85V to 132V, 187V to 264V; No. of Outputs:1; Output Voltage Nom.:24V; Output Current Max:10A; Output Power Max:240W ;RoHS Compliant: Yes 制造商:Traco Power 功能描述:DIN Rail PSU 24Vdc, 240W, 10A |

| TSPC480-124 | 制造商:Traco Power 功能描述:AC-DC CONV, DIN RAIL, 1 O/P, 480W, 20A, 24V; Power Supply Output Type:Adjustable, Fixed; Input Voltage VAC:85V to 132V, 187V to 264V; No. of Outputs:1; Output Voltage Nom.:24V; Output Current Max:20A; Output Power Max:480W ;RoHS Compliant: Yes 制造商:Traco Power 功能描述:DIN Rail PSU 24Vdc, 480W, 20A |

| TSPC603EMA5L | 制造商:e2v 功能描述: 制造商:e2v technologies 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。