- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376425 > UPD30550F2-400-NN1 (NEC Corp.) VR5500⑩ 64-/32-BIT MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | UPD30550F2-400-NN1 |

| 廠商: | NEC Corp. |

| 英文描述: | VR5500⑩ 64-/32-BIT MICROPROCESSOR |

| 中文描述: | VR5500⑩64-/32-BIT微處理器 |

| 文件頁數(shù): | 10/27頁 |

| 文件大小: | 569K |

| 代理商: | UPD30550F2-400-NN1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

Data Sheet U15700EJ1V0DS

10

μ

PD30550

(2/2)

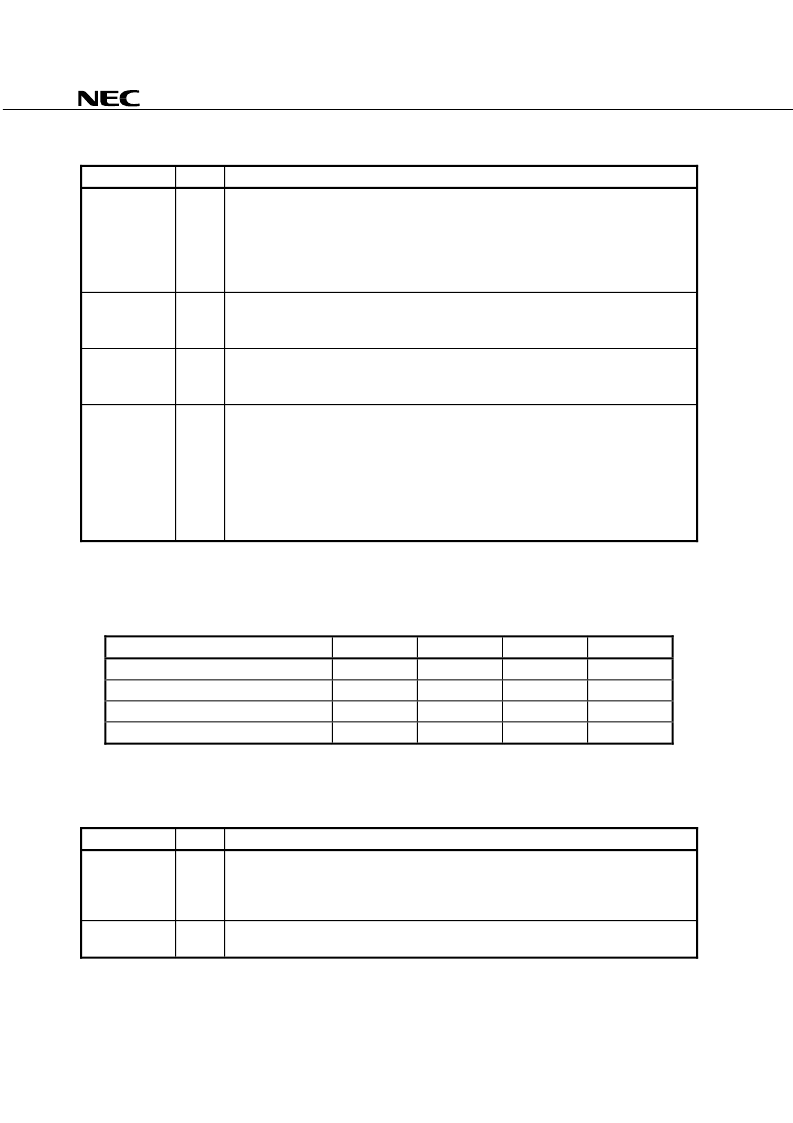

Pin Name

I/O

Function

O3Return#

Input

Out-of-Order Return mode

This signal sets the protocol of the system interface.

1: Normal mode

0: Out-of-order return mode

Set the input level of this signal before a power-on reset. Make sure that the level of this signal

does not change during VR5500 operation.

ColdReset#

Input

Cold reset

This signal completely initializes the internal status of the processor. Deassert it in

synchronization with SysClock.

Reset#

Input

Reset

This signal logically initializes the internal status of the processor. Deassert it in synchronization

with SysClock.

DrvCon

Input

Drive control

This signal sets the impedance of the external output driver.

1: Low

0: Normal (recommended)

Set the input level of this signal before a power-on reset. Make sure that the level of this signal

does not change during VR5500 operation.

Remark

Applies to revision 2.0 or later products. Fixed to 0 in revision 1.x products.

Remark

1: High level, 0: Low level

The O3Return#, DWBTrans#, DisDValidO#, and BusMode signals are used for determining the protocol of the system

interface. The protocol is selected as follows in accordance with the setting of these signals.

Protocol

O3Return#

DWBTrans#

DisDValidO#

BusMode

V

R

5000

TM

compatible

1

1

1

1

RM523x compatible

1

1

1

0

V

R

5432 native mode compatible

1

0

0

0

Out-of-order return mode

0

Arbitrary

Arbitrary

Arbitrary

Remark

1: High level, 0:Low level

RM523x is a product of PMC-Sierra, Inc.

(3) Interrupt interface signals

Pin Name

I/O

Function

Int(5:0)#

Input

Interrupt

These are general-purpose processor interrupt requests. The input states can be checked by

the Cause register.

Whether Int5# is acknowledged or not depends on the status of the TIntSel signal during reset.

NMI#

Input

Non-maskable interrupt

This is the non-maskable interrupt request.

相關PDF資料 |

PDF描述 |

|---|---|

| UPD4168 | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C-15 | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C-20 | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C-12 | 8,192 x 8-BIT NMOS XRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| UPD30700LRS-225 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30700LRS-250 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30700RS-180 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30700RS-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30710A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:VR Series Pamphlet | Pamphlet[12/2002] |

發(fā)布緊急采購,3分鐘左右您將得到回復。