- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376425 > UPD30550F2-400-NN1 (NEC Corp.) VR5500⑩ 64-/32-BIT MICROPROCESSOR PDF資料下載

參數(shù)資料

| 型號: | UPD30550F2-400-NN1 |

| 廠商: | NEC Corp. |

| 英文描述: | VR5500⑩ 64-/32-BIT MICROPROCESSOR |

| 中文描述: | VR5500⑩64-/32-BIT微處理器 |

| 文件頁數(shù): | 18/27頁 |

| 文件大小: | 569K |

| 代理商: | UPD30550F2-400-NN1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

Data Sheet U15700EJ1V0DS

18

μ

PD30550

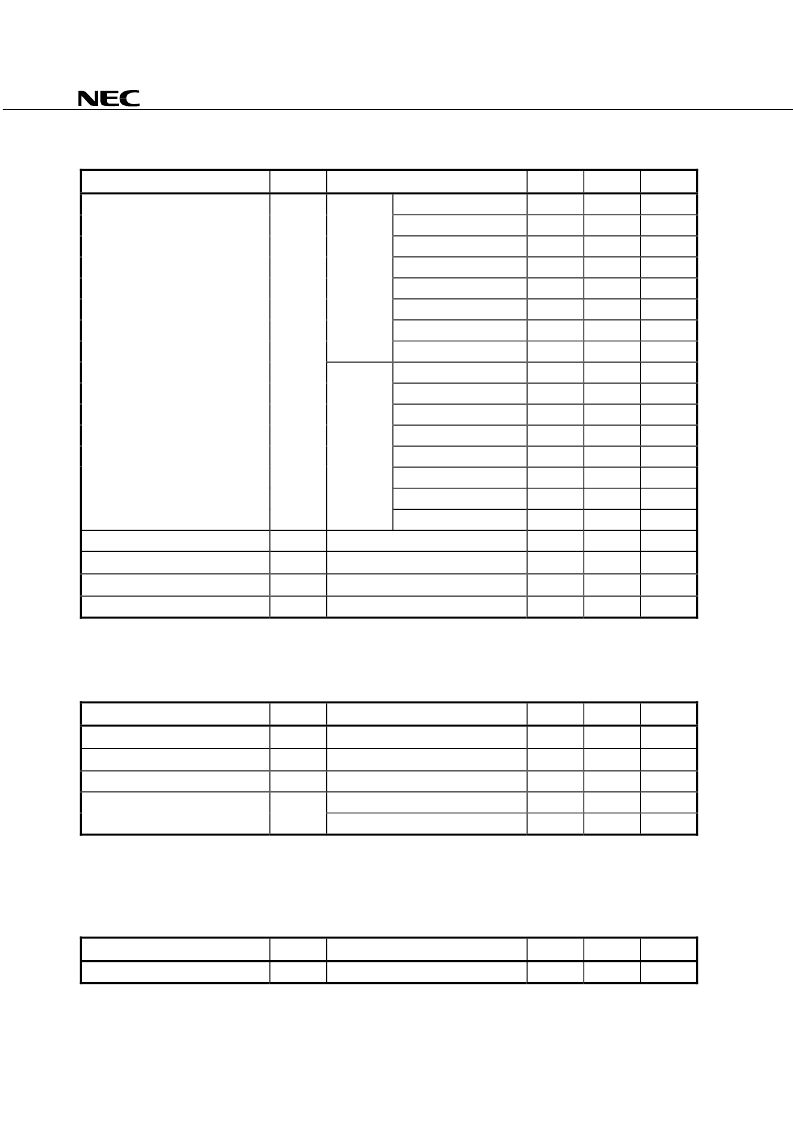

Clock parameters (2/2)

Parameter

Symbol

Conditions

MIN.

MAX.

Unit

DivMode = 2:1

7.5

10

ns

DivMode = 2.5:1

8.3

12.5

ns

DivMode = 3:1

10

15

ns

DivMode = 3.5:1

11.7

17.5

ns

DivMode = 4:1

13.3

20

ns

DivMode = 4.5:1

15

22.5

ns

DivMode = 5:1

16.7

25

ns

300 MHz

product

DivMode = 5.5:1

18.3

27.5

ns

DivMode = 2:1

7.5

10

ns

DivMode = 2.5:1

7.5

12.5

ns

DivMode = 3:1

7.5

15

ns

DivMode = 3.5:1

8.8

17.5

ns

DivMode = 4:1

10

20

ns

DivMode = 4.5:1

11.3

22.5

ns

DivMode = 5:1

12.5

25

ns

System clock cycle

t

CP

400 MHz

product

DivMode = 5.5:1

13.8

27.5

ns

System clock jitter

t

J

5

%

System clock rise time

t

CR

1.2

ns

System clock fall time

t

CF

1.2

ns

JTAG clock frequency

33

MHz

Remarks 1.

The system clock jitter is a cycle-to-cycle jitter.

2.

The JTAG clock runs asynchronously to the system clock.

System interface parameters

Parameter

Symbol

Conditions

MIN.

MAX.

Unit

Data output hold time

Note 1

t

DM

1.0

ns

Data output delay time

Note 1

t

DO

5.0

ns

Data input setup time

Note 2

t

DS

1.5

ns

300 MHz product

1.0

ns

Data input hold time

Note 2

t

DH

400 MHz product

0.5

ns

Notes 1.

Applies to the Release#, ValidOut#, SysAD(63:0), SysADC(7:0), SysCmd(8:0), and SysID(2:0) pins.

2.

Applies to the ColdReset#, Reset#, Int(5:0), NMI#, ExtRqst#, RdRdy#, ValidIn#, SysAD(63:0),

SysADC(7:0), SysCmd(8:0), and SysID(2:0) pins.

Load coefficient

Parameter

Symbol

Conditions

MIN.

MAX.

Unit

Load coefficient

CLD

1.0

ns/25 pF

相關PDF資料 |

PDF描述 |

|---|---|

| UPD4168 | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C-15 | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C-20 | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C | 8,192 x 8-BIT NMOS XRAM |

| UPD4168C-12 | 8,192 x 8-BIT NMOS XRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| UPD30700LRS-225 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30700LRS-250 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30700RS-180 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30700RS-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| UPD30710A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:VR Series Pamphlet | Pamphlet[12/2002] |

發(fā)布緊急采購,3分鐘左右您將得到回復。