- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378747 > UPD75336GK (NEC Corp.) 4-BIT SINGLE-CHIP MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | UPD75336GK |

| 廠商: | NEC Corp. |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| 中文描述: | 4位單片機(jī) |

| 文件頁數(shù): | 40/68頁 |

| 文件大小: | 532K |

| 代理商: | UPD75336GK |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

40

μ

PD75336

MB = MBE MBS (MBS = 0, 1, 2, 15)

MB = 0

MBE = 0 : MB = 0 (000H to 07FH)

MB = 15 (F80H to FFFH)

MBE = 1 : MB = MBS (MBS = 0, 1, 2, 15)

MB = 15, fmem = FB0H to FBFH,

FF0H to FFFH

MB = 15, pmem = FC0H to FFFH

addr = 0000H to 3F7FH

addr = (Current PC) –15 to (Current PC) –1

(Current PC) + 2 to (Current PC) + 16

caddr = 0000H to 0FFFH (PC

13, 12

= 00B) or

1000H to 1FFFH (PC

13, 12

= 01B) or

2000H to 2FFFH (PC

13, 12

= 10B) or

3000H to 3F7FH (PC

13, 12

= 11B)

faddr = 0000H to 07FFH

taddr = 0020H to 007FH

(3)

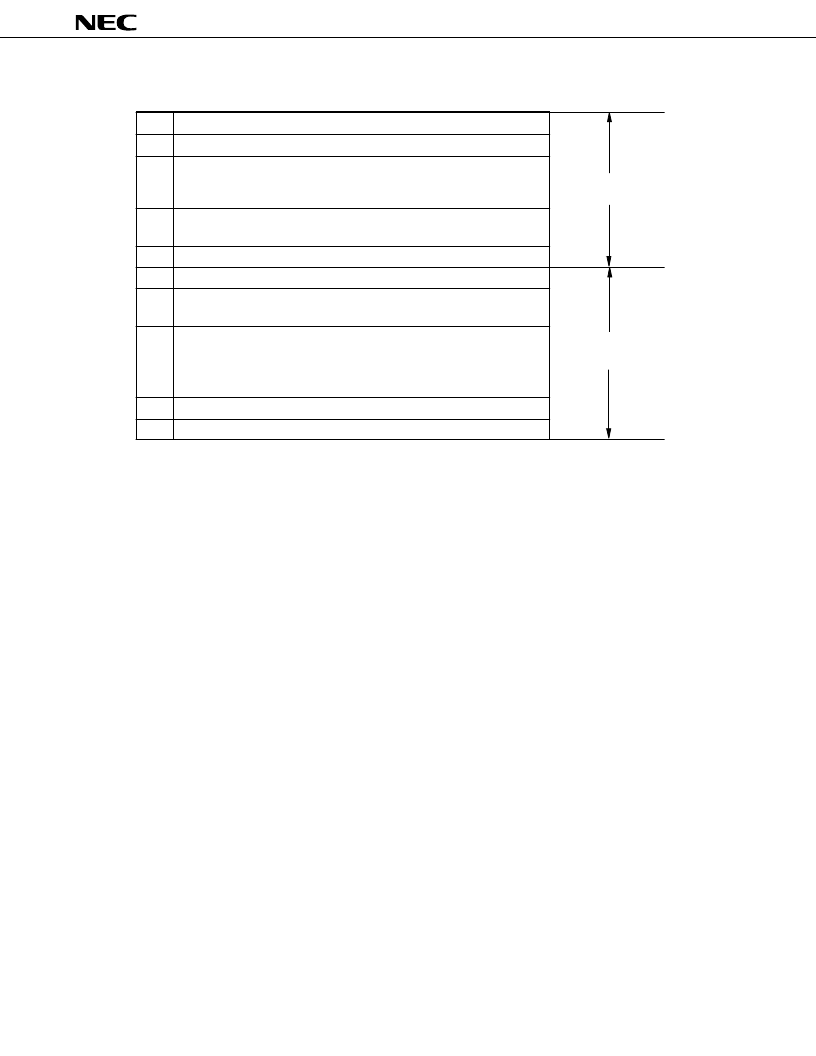

Description of symbols in the addressing area column

*1

*2

*3

*4

*5

*6

*7

*8

*9

*10

Data memory

addressing

Program memory

addressing

Remarks

1.

2.

3.

4.

MB indicates an accessible memory bank.

In *2, MB = 0 irrespective of MBE and MBS.

In *4 and *5, MB = 15 irrespective of MBE and MBS.

*6 to *10 indicate addressable areas.

(4)

Description of machine cycle column

S indicates the number of machine cycles required for an instruction with skip function to carry out skip operation.

The value of S varies as follows:

When not skipped ...................................................................................................................................

When the skipped instruction is a 1-byte or 2-byte instruction .......................................................

When the skipped instruction is a 3-byte instruction (BR !adder, CALL !adder instructions) .....

S = 0

S = 1

S = 2

Note

GETI instruction is skipped in a 1 machine cycle.

The 1 machine cycle is equal to one cycle of CPU clock

Φ

(=t

CY

) and four time periods are selectable by setting

the PCC.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD75336 | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD754244 | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD754244GS | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD75512 | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75512A | 4-BIT SINGLE-CHIP MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD7554AG-597-E2 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7554AG-597-E2-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7554AG-603-E2 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7554AG-603-E2-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7554AG-611-E2 | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。