- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359354 > VDP3108 (MICRONAS SEMICONDUCTOR HOLDING AG) Single-Chip Video Processor PDF資料下載

參數(shù)資料

| 型號: | VDP3108 |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Single-Chip Video Processor |

| 中文描述: | 單芯片視頻處理器 |

| 文件頁數(shù): | 17/61頁 |

| 文件大小: | 2638K |

| 代理商: | VDP3108 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

ADVANCE INFORMATION

VDP 3108

MICRONAS INTERMETALL

17

noise amplitudes in the correction signal are suppressed

by an adjustable coring circuit. To eliminate ‘wrong col-

ors’ , which are caused by over and undershoots at the

chroma transition, the sharpened chroma signals are

limited to a proper value automatically.

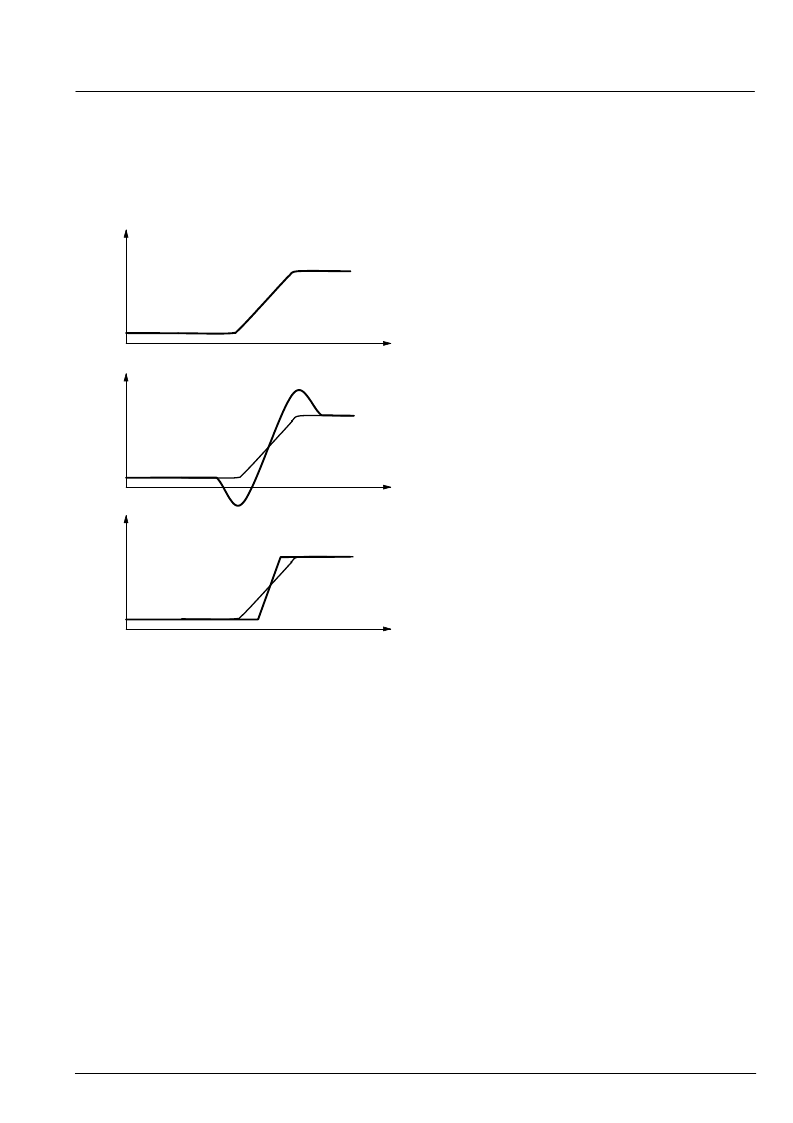

Fig. 2–21:

Digital Color Transient Improvement

t

t

t

Cr out

Cb out

Ampl.

Cr in

Cb in

a)

b)

c)

a) Cr Cb input of DTI

b) Cr Cb input + Correction signal

c) sharpened and limited Cr Cb

2.4.8. Dematrix

A 6-multiplier matrix transcodes the Cr and Cb signals

to R–Y, B–Y and G–Y. The multipliers are also used to

adjust color saturation in the range of 0 ... 2. The coeffi-

cients are signed and have a resolution of 9 bits. The

matrix coefficients are separate for main and side pic-

ture. The matrix computes:

R–Y =

G–Y =

B–Y

MR1*Cb + MR2*Cr

MG1*Cb + MG2*Cr

MB1*Cb + MB2*Cr

=

The initialization values for the matrix are computed

from the standard ITUR matrix:

R

G

B

1

1

1

0

0.345

1.773

1.402

0.713

0

Y

Cb

Cr

For a contrast setting of CTM=32 the matrix values are

scaled by a factor of 64, see also table 3–1.

2.4.9. RGB Processing

After adding the post processed luma, the digital RGBs

are limited to 10 bits. Three multipliers are used to digi-

tally adjust the whitedrive. Using the same multipliers an

average beam current limiter is implemented. See also

paragraph ‘CRT control’.

2.4.10. FIFO Display Buffer

A FIFO is used to buffer the phase differences between

the video source and the flyback signal. By using the de-

scribed clock system, this ‘phase-buffer‘ is working with

sub-pixel accuracy. It has a range of 8 clocks which is

equivalent to +/– 200 ns @ 20.25 MHz.

2.5. Analog Back End

The digital RGB signals are converted to analog RGBs

using three video digital to analog converters (DAC) with

10 bit resolution. An analog brightness value is provided

by three additional DACs. The adjustment range is 40%

of the full RGB range.

The back end allows insertion of an external analog

RGB signal. The RGB signal is key-clamped and in-

serted into the main RGB by the fast blank switch. The

external RGB signals are virtually handled as priority

bus signals. Thus they can be overlaid or underlaid to

the digital picture. The external RGB signals can be in-

dependently adjusted in DC-level (brightness) and mag-

nitude (contrast).

The controls for the whitedrive / analog brightness and

also for the external contrast and brightness adjust-

ments are via the Fast Processor. The controls for the

cutoff DACs are via I

2

C bus registers.

Finally cutoff and blanking values are added to the RGB

signals. Cutoff (dark current) is provided by three 9-bit

DACs. The adjustment range is 60% of full scale RGB

range.

The analog RGB-outputs are current outputs with cur-

rent-sink characteristics. The maximum current drawn

by the output stage is obtained with peak white RGB.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VDP3130Y | Video Processor Family |

| VDP31XXB | Video Processor Family |

| VDP3108PR | Consumer IC |

| VDSGLD_38.88 | TRANS PREBIASED PNP 200MW SOT23 |

| VDSL5100I | TVS 400W 43V UNIDIRECT SMA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VDP3108B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3108PR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Consumer IC |

| VDP3112B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3116B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

| VDP3120B | 制造商:MICRONAS 制造商全稱:MICRONAS 功能描述:Video Processor Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。