- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19901 > XC18V04PC44C (Xilinx Inc)IC PROM SER C-TEMP 3.3V 44-PLCC PDF資料下載

參數(shù)資料

| 型號(hào): | XC18V04PC44C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 5/24頁(yè) |

| 文件大小: | 0K |

| 描述: | IC PROM SER C-TEMP 3.3V 44-PLCC |

| 標(biāo)準(zhǔn)包裝: | 26 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程 |

| 存儲(chǔ)容量: | 4Mb |

| 電源電壓: | 3 V ~ 3.6 V |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 44-PLCC(16.59x16.59) |

| 包裝: | 管件 |

| 其它名稱: | 122-1274 XC18V04PC44C-ND |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

XC18V00 Series In-System-Programmable Configuration PROMs

DS026 (v5.2) January 11, 2008

Product Specification

13

R

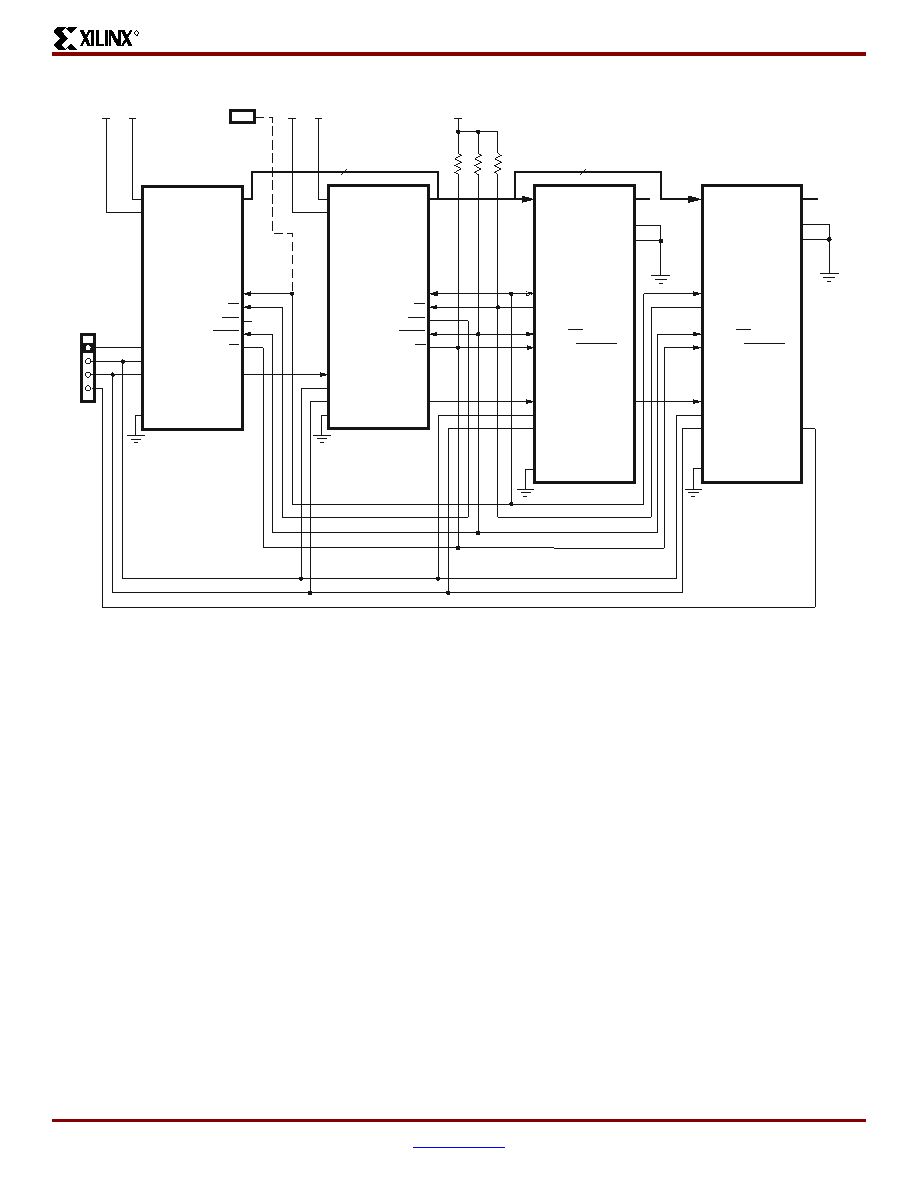

X-Ref Target - Figure 8

Figure 8: Configuring Multiple Devices with Identical Patterns in Master/Slave Serial,

Master/Slave SelectMAP, or Master/Slave Parallel Mode

XC18V00

PROM

First

PROM

(PROM 0)

VCCINT

VCCO

(2)

TDI

TMS

TCK

GND

D[0:7](3)

CLK

CE

CEO

OE/RESET

CF

TDO

Xilinx FPGA

Master

Serial/SelectMAP

Xilinx FPGA

Slave

Serial/SelectMAP

D[0:7]

(3)

CCLK

DONE

INIT_B (INIT)

PROG_B (PROGRAM)

TDI

TMS

TCK

GND

MODE PINS

(1)

TDO

4.7

k

Ω

4.7

k

Ω

(1)

VCCO

(2)

TDI

TMS

TCK

TDO

Notes:

1 For MODE pin connections and DONE pin pullup value, refer to the appropriate FPGA data sheet or user guide.

2 For compatible voltages, refer to the appropriate data sheet.

3 Serial modes do not require the D[1:7], RDWR_B, or CS_B pins to be connected.

4 External oscillator required if CLK is not supplied by an FPGA in Master mode. Refer to the appropriate FPGA data sheet.

D[0:7]

(3)

CCLK

DONE

INIT_B (INIT)

PROG_B (PROGRAM)

TDI

TMS

TCK

GND

XC18V00

PROM

Cascaded

PROM

(PROM 1)

VCCINT

VCCO

(2)

TDI

TMS

TCK

GND

D[0:7](3)

CLK

CE

CEO

OE/RESET

CF

TDO

MODE PINS

(1)

TDO

DS026_17_111207

RDWR_B

(3)

CS_B

(3)

RDWR_B

(3)

CS_B

(3)

VCCO VCCINT

External (4)

Oscillator

8

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AGM22DTMH | CONN EDGECARD 44POS R/A .156 SLD |

| XC17V04PC44I | IC PROM SER 4MBIT 3.3V 44-PLCC |

| RSA36DRSZ-S664 | CONN EDGECARD 72POS DIP .125 SLD |

| XC17V04PC20I | IC PROM SER 4MBIT 3.3V 20-PLCC |

| T95R336M035EAAS | CAP TANT 33UF 35V 20% 2824 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC18V04-PC44C | 制造商:Xilinx 功能描述: |

| XC18V04PC44C0100 | 制造商:Xilinx 功能描述: |

| XC18V04PC44C0901 | 制造商:Xilinx 功能描述: |

| XC18V04PC44C0936 | 制造商:Xilinx 功能描述:XLXXC18V04PC44C0936 IC SYSTEM GATE |

| XC18V04PC44C1 | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。