- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4277 > XC3S500E-5FGG320C (Xilinx Inc)IC FPGA SPARTAN-3E 500K 320-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S500E-5FGG320C |

| 廠(chǎng)商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 169/227頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 320-FBGA |

| 標(biāo)準(zhǔn)包裝: | 84 |

| 系列: | Spartan®-3E |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 232 |

| 門(mén)數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 320-BGA |

| 供應(yīng)商設(shè)備封裝: | 320-FBGA(19x19) |

| 配用: | 122-1536-ND - KIT STARTER SPARTAN-3E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)當(dāng)前第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)

Spartan-3E FPGA Family: Functional Description

DS312 (v4.1) July 19, 2013

Product Specification

46

Multiplier/Block RAM Interaction

Each multiplier is located adjacent to an 18 Kbit block RAM

and shares some interconnect resources. Configuring an

18 Kbit block RAM for 36-bit wide data (512 x 36 mode)

prevents use of the associated dedicated multiplier.

The upper 16 bits of the ‘A’ multiplicand input are shared

with the upper 16 bits of the block RAM’s Port A Data input.

Similarly, the upper 16 bits of the ‘B’ multiplicand input are

shared with Port B’s data input. See also Figure 48,

Table 27 defines each port of the MULT18X18SIO primitive.

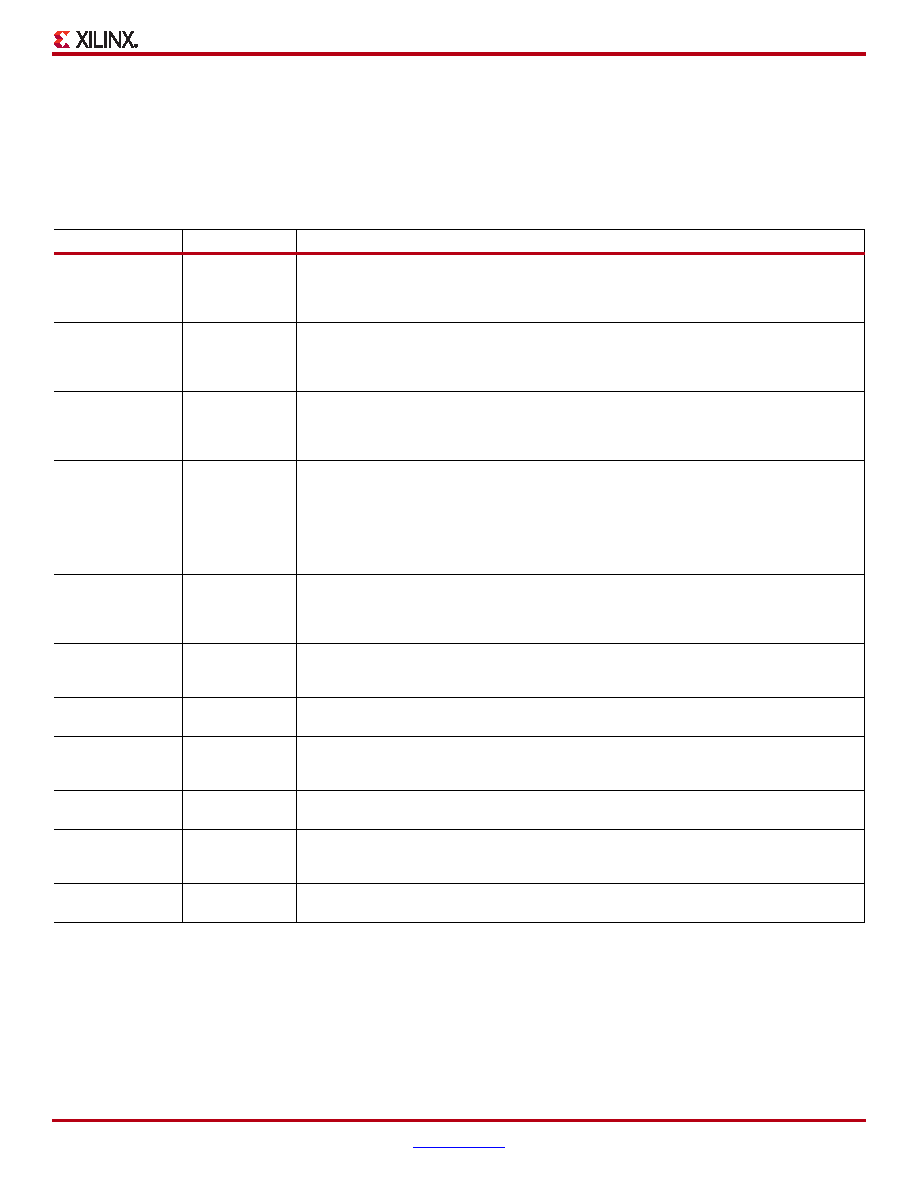

Table 27: MULT18X18SIO Embedded Multiplier Primitives Description

Signal Name

Direction

Function

A[17:0]

Input

The primary 18-bit two’s complement value for multiplication. The block multiplies by this value

asynchronously if the optional AREG and PREG registers are omitted. When AREG and/or

PREG are used, the value provided on this port is qualified by the rising edge of CLK, subject

to the appropriate register controls.

B[17:0]

Input

The second 18-bit two’s complement value for multiplication if the B_INPUT attribute is set to

DIRECT. The block multiplies by this value asynchronously if the optional BREG and PREG

registers are omitted. When BREG and/or PREG are used, the value provided on this port is

qualified by the rising edge of CLK, subject to the appropriate register controls.

BCIN[17:0]

Input

The second 18-bit two’s complement value for multiplication if the B_INPUT attribute is set to

CASCADE. The block multiplies by this value asynchronously if the optional BREG and PREG

registers are omitted. When BREG and/or PREG are used, the value provided on this port is

qualified by the rising edge of CLK, subject to the appropriate register controls.

P[35:0]

Output

The 36-bit two’s complement product resulting from the multiplication of the two input values

applied to the multiplier. If the optional AREG, BREG and PREG registers are omitted, the

output operates asynchronously. Use of PREG causes this output to respond to the rising edge

of CLK with the value qualified by CEP and RSTP. If PREG is omitted, but AREG and BREG

are used, this output responds to the rising edge of CLK with the value qualified by CEA, RSTA,

CEB, and RSTB. If PREG is omitted and only one of AREG or BREG is used, this output

responds to both asynchronous and synchronous events.

BCOUT[17:0]

Output

The value being applied to the second input of the multiplier. When the optional BREG register

is omitted, this output responds asynchronously in response to changes at the B[17:0] or

BCIN[17:0] ports according to the setting of the B_INPUT attribute. If BREG is used, this output

responds to the rising edge of CLK with the value qualified by CEB and RSTB.

CEA

Input

Clock enable qualifier for the optional AREG register. The value provided on the A[17:0] port is

captured by AREG in response to a rising edge of CLK when this signal is High, provided that

RSTA is Low.

RSTA

Input

Synchronous reset for the optional AREG register. AREG content is forced to the value zero in

response to a rising edge of CLK when this signal is High.

CEB

Input

Clock enable qualifier for the optional BREG register. The value provided on the B[17:0] or

BCIN[17:0] port is captured by BREG in response to a rising edge of CLK when this signal is

High, provided that RSTB is Low.

RSTB

Input

Synchronous reset for the optional BREG register. BREG content is forced to the value zero in

response to a rising edge of CLK when this signal is High.

CEP

Input

Clock enable qualifier for the optional PREG register. The value provided on the output of the

multiplier port is captured by PREG in response to a rising edge of CLK when this signal is High,

provided that RSTP is Low.

RSTP

Input

Synchronous reset for the optional PREG register. PREG content is forced to the value zero in

response to a rising edge of CLK when this signal is High.

Notes:

1.

The control signals CLK, CEA, RSTA, CEB, RSTB, CEP, and RSTP have the option of inverted polarity.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3S500E-4FGG320I | IC FPGA SPARTAN-3E 500K 320-FBGA |

| XC6SLX25-N3CSG324C | IC FPGA SPARTAN-6 324CSBGA |

| 93LC86CT-I/MNY | IC EEPROM SER 16K 2.5V 8TDFN |

| XC6SLX25-N3FTG256I | IC FPGA SPARTAN-6 256FBGA |

| XC6SLX25-2FT256I | IC FPGA SPARTAN 6 256FTGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S500E-5FT256C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 500K GATES 10476 CELLS 657MHZ 90NM 1.2V 256F - Trays |

| XC3S500E-5FTG256C | 功能描述:IC FPGA SPARTAN-3E 500K 256FTBGA RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門(mén)數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類(lèi)型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S500E-5PQ208C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 500K GATES 10476 CELLS 657MHZ 90NM 1.2V 208P - Trays |

| XC3S500E-5PQG208C | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門(mén)數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類(lèi)型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱(chēng):220-1241 |

| XC3S50-4CP132I | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。