- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4169 > XC5210-6PQ240C (Xilinx Inc)IC FPGA 324 CLB'S 240-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC5210-6PQ240C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 34/73頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 324 CLB'S 240-PQFP |

| 產(chǎn)品變化通告: | XC1700 PROMs,XC5200,HQ,SCD Parts Discontinuation 19/Jul/2010 |

| 標準包裝: | 24 |

| 系列: | XC5200 |

| LAB/CLB數(shù): | 324 |

| 邏輯元件/單元數(shù): | 1296 |

| 輸入/輸出數(shù): | 196 |

| 門數(shù): | 16000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 240-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 240-PQFP(32x32) |

| 其它名稱: | 122-1151 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

XC5200 Series Field Programmable Gate Arrays

7-86

November 5, 1998 (Version 5.2)

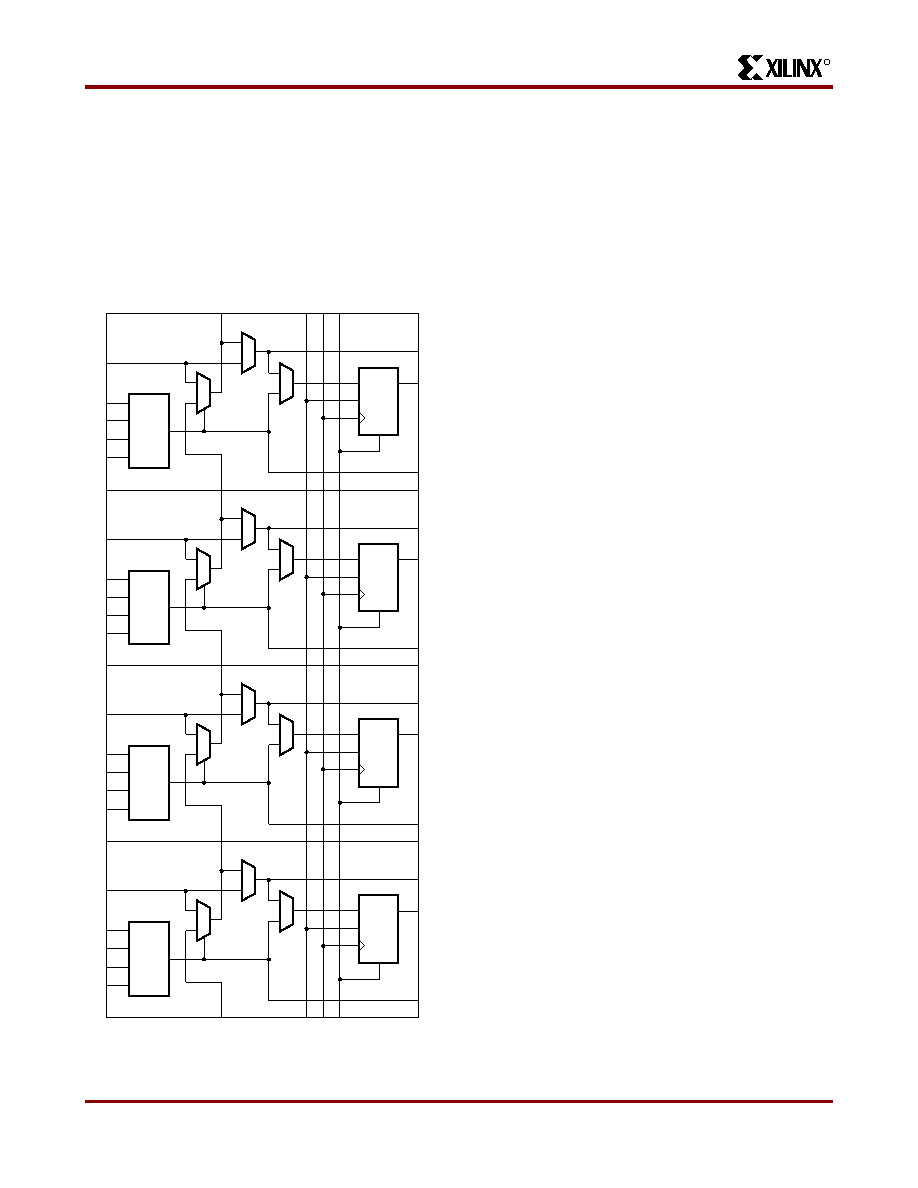

The XC5200 CLB consists of four LCs, as shown in

Figure 4. Each CLB has 20 independent inputs and 12

independent outputs. The top and bottom pairs of LCs can

be configured to implement 5-input functions. The chal-

lenge of FPGA implementation software has always been

to maximize the usage of logic resources. The XC5200

family addresses this issue by surrounding each CLB with

two types of local interconnect — the Local Interconnect

Matrix (LIM) and direct connects. These two interconnect

resources, combined with the CLB, form the VersaBlock,

represented in Figure 2.

The LIM provides 100% connectivity of the inputs and out-

puts of each LC in a given CLB. The benefit of the LIM is

that no general routing resources are required to connect

feedback paths within a CLB. The LIM connects to the

GRM via 24 bidirectional nodes.

The direct connects allow immediate connections to neigh-

boring CLBs, once again without using any of the general

interconnect. These two layers of local routing resource

improve the granularity of the architecture, effectively mak-

ing the XC5200 family a “sea of logic cells.” Each

Versa-Block has four 3-state buffers that share a common

enable line and directly drive horizontal and vertical Lon-

glines, creating robust on-chip bussing capability. The

VersaBlock allows fast, local implementation of logic func-

tions, effectively implementing user designs in a hierarchi-

cal fashion. These resources also minimize local routing

congestion and improve the efficiency of the general inter-

connect, which is used for connecting larger groups of

logic. It is this combination of both fine-grain and

coarse-grain architecture attributes that maximize logic uti-

lization in the XC5200 family. This symmetrical structure

takes full advantage of the third metal layer, freeing the

placement software to pack user logic optimally with mini-

mal routing restrictions.

VersaRing I/O Interface

The interface between the IOBs and core logic has been

redesigned in the XC5200 family. The IOBs are completely

decoupled from the core logic. The XC5200 IOBs contain

dedicated boundary-scan logic for added board-level test-

ability, but do not include input or output registers. This

approach allows a maximum number of IOBs to be placed

around the device, improving the I/O-to-gate ratio and

decreasing the cost per I/O. A “freeway” of interconnect

cells surrounding the device forms the VersaRing, which

provides connections from the IOBs to the internal logic.

These incremental routing resources provide abundant

connections from each IOB to the nearest VersaBlock, in

addition to Longline connections surrounding the device.

The VersaRing eliminates the historic trade-off between

high logic utilization and pin placement flexibility. These

incremental edge resources give users increased flexibility

in preassigning (i.e., locking) I/O pins before completing

their logic designs. This ability accelerates time-to-market,

since PCBs and other system components can be manu-

factured concurrent with the logic design.

General Routing Matrix

The GRM is functionally similar to the switch matrices

found in other architectures, but it is novel in its tight cou-

pling to the logic resources contained in the VersaBlocks.

Advanced simulation tools were used during the develop-

ment of the XC5200 architecture to determine the optimal

level of routing resources required. The XC5200 family

contains six levels of interconnect hierarchy — a series of

Figure 4: Configurable Logic Block

X4957

F4

F3

F

FD

LC3

LC2

LC1

LC0

F2

F1

DQ

X

DO

DI

CO

F4

F3

F

FD

F2

F1

DQ

X

DO

DI

F4

F3

F

FD

F2

F1

DQ

X

DO

DI

F4

F3

F

FD

F2

F1

DQ

X

DO

DI

CI

CE CK

CLR

LC0

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5210-5PQ240C | IC FPGA 324 CLB'S 240-PQFP |

| XC5210-6PQ208C | IC FPGA 324 CLB'S 208-PQFP |

| 88997-2 | CONTACT TIN SOLDER FLAT FLEX |

| ABC65DREI-S93 | CONN EDGECARD 130PS .100 EYELET |

| GMC22DTEF | CONN EDGECARD 44POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-6PQ240I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-6PQG208C | 制造商:Xilinx 功能描述: |

| XC52106T144C | 制造商:Xilinx 功能描述: |

| XC5210-6TQ144C | 功能描述:IC FPGA 324 CLB'S 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC5200 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XC5210-6TQ144I | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。