- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376454 > XR17C158 (Exar Corporation) PCI Bus Octal UART(八通用異步接收器/發(fā)送器(滿足通訊系統(tǒng)中PCI總線和高帶寬要求)) PDF資料下載

參數(shù)資料

| 型號(hào): | XR17C158 |

| 廠商: | Exar Corporation |

| 英文描述: | PCI Bus Octal UART(八通用異步接收器/發(fā)送器(滿足通訊系統(tǒng)中PCI總線和高帶寬要求)) |

| 中文描述: | PCI總線八路的UART(八通用異步接收器/發(fā)送器(滿足通訊系統(tǒng)中的PCI總線和高帶寬要求)) |

| 文件頁數(shù): | 29/51頁 |

| 文件大?。?/td> | 685K |

| 代理商: | XR17C158 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

XR17C158

PCI BUS OCTAL UART

PRELIMINARY

REV. 1.0.0

29

N

OTE

:

MCR bits 2 and 3 (OP1 and OP2 outputs) are not

available in the XR17C158. They are present for 16C550

compatibility during Internal loopback, see

Figure 11

.

4.6

T

RANSMITTER

The transmitter section comprises of a 64 bytes of

FIFO, a byte-wide Transmit Holding Register (THR)

and a 8-bit Transmit Shift Register (TSR). THR re-

ceives a data byte from the host (non-FIFO mode) or

a data byte from the FIFO

when the FIFO is enabled

by FCR bit-0. TSR shifts out every data bit with the

16X or 8X internal clock. A bit time is 16 or 8 clock pe-

riods. The transmitter sends the start bit followed by

the number of data bits, inserts the proper parity bit if

enable, and adds the stop bit(s). The status of the

THR and TSR are reported in the Line Status Regis-

ter (LSR bit-5 and bit-6).

4.6.1

Transmit Holding Register (THR)

The transmit holding register is a 8-bit register provid-

ing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted

into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (Bit-

0) becomes first data bit to go out. The THR is also

the input register to the transmit FIFO of 64 bytes

when FIFO operation is enabled by FCR bit-0. A THR

empty interrupt can be generated when it is enabled

in IER bit-1.

4.6.2

Transmitter Operation in non-FIFO

The host loads transmit data to THR one character at

a time. The THR empty flag (LSR bit-5) is set when

the data byte is transferred to TSR. THR flag can

generate a transmit empty interrupt (ISR bit-1) when

it is enabled by IER bit-1. The TSR flag (LSR bit-6) is

set when TSR becomes completely empty.

4.6.3

The host may fill the transmit FIFO with up to 64

bytes of transmit data. The THR empty flag (LSR bit-

5) is set whenever the FIFO is empty. The THR emp-

ty flag can generate a transmit empty interrupt (ISR

bit-1) when the amount of data in the FIFO falls below

its programmed trigger level (see TXTRG register).

The transmit empty interrupt is enabled by IER bit-1.

The TSR flag (LSR bit-6) is set when TSR becomes

completely empty. Furthermore, with the RS485 half-

duplex direction control enabled (FCTR bit-5=1) the

source of the transmit empty interrupt changes to

TSR empty instead of THR empty. This is to ensure

the RTS# output is not changed until the last stop bit

of the last character is shifted out.

Transmitter Operation in FIFO

4.6.4

The auto RS485 half-duplex direction control chang-

es the behavior of the transmitter when enabled by

FCTR bit-5. It de-asserts RTS# or DTR# after a spec-

ified delay indicated in MSR[7:4] following

the last

stop bit of the last character that has been transmit-

ted. This helps in turning around the transceiver to re-

ceive the remote station’s response. The delay opti-

mizes the time needed for the last transmission to

reach the farthest station on a long cable network be-

fore switching off the line driver. This delay prevents

undesirable line signal disturbance that causes signal

degradation. It also changes the transmitter empty in-

terrupt to TSR empty instead of THR empty.

Auto RS485 Operation

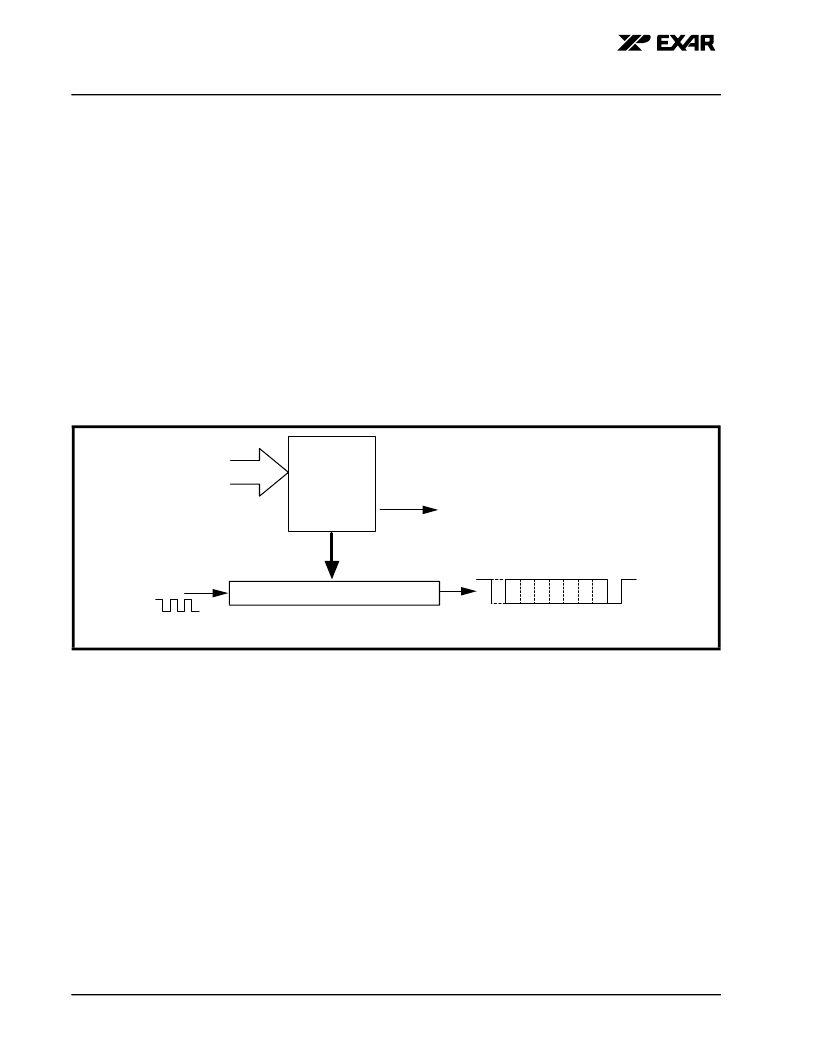

F

IGURE

12. T

RANSMITTER

O

PERATION

IN

NON

-FIFO M

ODE

Transmit

Holding

Register

(THR)

Transmit Shift Register (TSR)

Data

Byte

L

S

B

M

S

B

THR Interrupt (ISR bit-

1)

Enabled by IER bit-1

TXNOFIFO1

16X or 8X

Clock

(8XMODE

Register)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR17D152 | UNIVERSAL (3.3V AND 5V) PCI BUS DUAL UART |

| XR17D152CM | UNIVERSAL (3.3V AND 5V) PCI BUS DUAL UART |

| XR17D152IM | UNIVERSAL (3.3V AND 5V) PCI BUS DUAL UART |

| XR17D158IV | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| XR17D158 | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17C158CV | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C158CV-0A-EVB | 功能描述:UART 接口集成電路 Supports C158 144 ld TQFP, PCI Interface RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C158CV-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17C158CVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17C158CVTR-F |

| XR17C158IV | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。