- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376460 > XRT4500CV (EXAR CORP) MULTIPROTOCOL SERIAL NETWORK INTERFACE IC PDF資料下載

參數(shù)資料

| 型號: | XRT4500CV |

| 廠商: | EXAR CORP |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | MULTIPROTOCOL SERIAL NETWORK INTERFACE IC |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP80 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, TQFP-80 |

| 文件頁數(shù): | 43/99頁 |

| 文件大小: | 1384K |

| 代理商: | XRT4500CV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

XRT4500

MULTIPROTOCOL SERIAL NETWORK INTERFACE IC

REV. 1.0.7

á

40

1.2.1

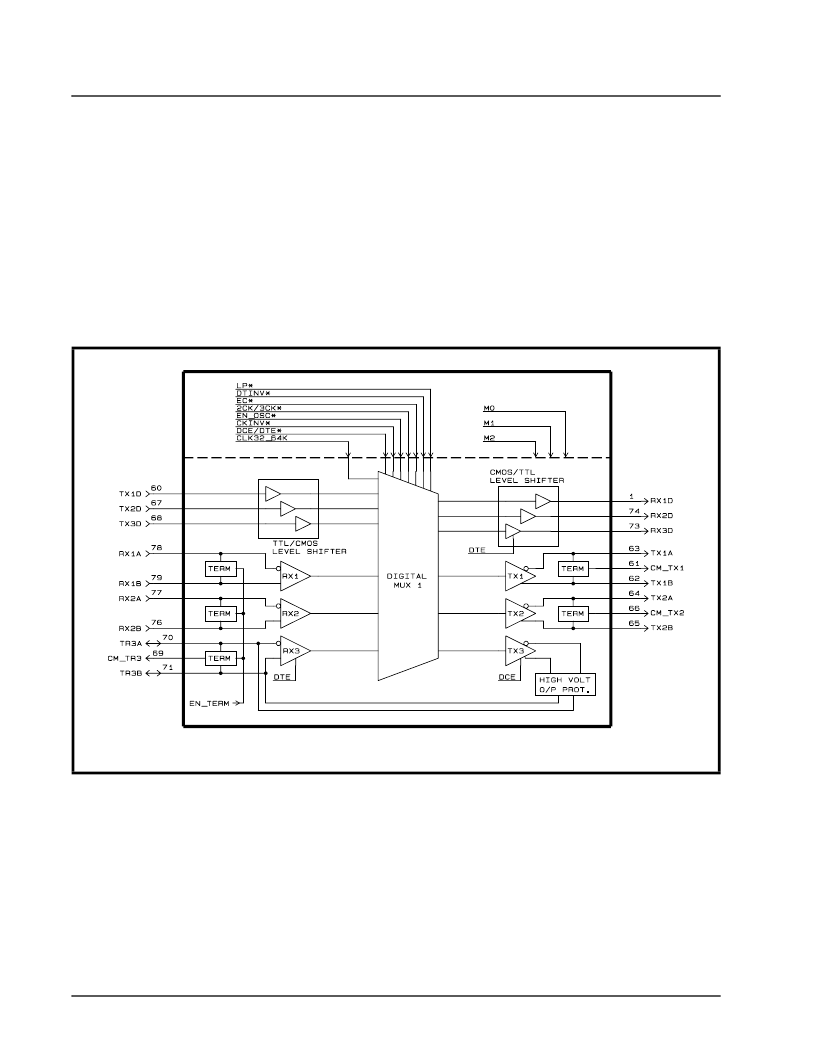

The “High-Speed Transceiver” block supports the

transmission and reception of high speed data and

clock signals for the selected “Communication Inter-

face”. This block contains receivers RX1 and RX2,

transmitters TX1 and TX2, and bi-directional trans-

ceiver TR3 which is composed of TX3 and RX3. Each

of these devices may be configured to support the

“Electrical Interface” requirements per ITU-T V.35,

ITU-T V.11 (EIA-422), ITU-T V.10 (EIA-423), or ITU-T

V.28 (EIA-232). In the “ITU-T V.35” Mode, each trans-

mitter has a common mode pin that is connected to

The “High -Speed Transceiver” Block

the center of the internal termination. This pin should

be bypassed to ground with an external 0.1μF capac-

itor in order to provide the best possible driver output

stage balance.

In a system application, the TX1-RX1 pair and TX2-RX2

pair handle the TXD-RXD (Transmit Data - Receive

Data) and the TXC-RXC (Transmit Clock - Receive

Clock) high speed interface signals respectively. Trans-

ceiver TR3 is dedicated to the SCTE (Transmit Clock

Echo) signal for both DCE and DTE modes of operation.

Transceiver TR3 functions as a receiver for the DTE

mode and as a transmitter during the DCE mode.

F

IGURE

12. H

IGH

-S

PEED

T

RANSCEIVER

B

LOCK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT56L85 | Low Power PCM Line Interface |

| XRT5794ES | Evaluation System |

| XRT5894ES | () |

| XRT5894 | Four-Channel E1 Line Interface (3.3V or 5.0V)(四通道E1 3.3V線接口單元) |

| XRT5897ES | () |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR-T5600P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Repeater |

| XR-T56188CD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Transceiver |

| XR-T56188CP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Transceiver |

| XR-T56188ID | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Transceiver |

| XR-T56188IP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。