- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75L04DIV (EXAR CORP) FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號: | XRT75L04DIV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | ATM/SONET/SDH SUPPORT CIRCUIT, PQFP176 |

| 封裝: | 24 X 24 MM, 1.40 MM HEIGHT, TQFP-176 |

| 文件頁數(shù): | 91/98頁 |

| 文件大?。?/td> | 536K |

| 代理商: | XRT75L04DIV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁當(dāng)前第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

á

REV. 1.0.1

XRT75L04D

FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

87

HOW MAJOR PATTERN B IS SYNTHESIZED

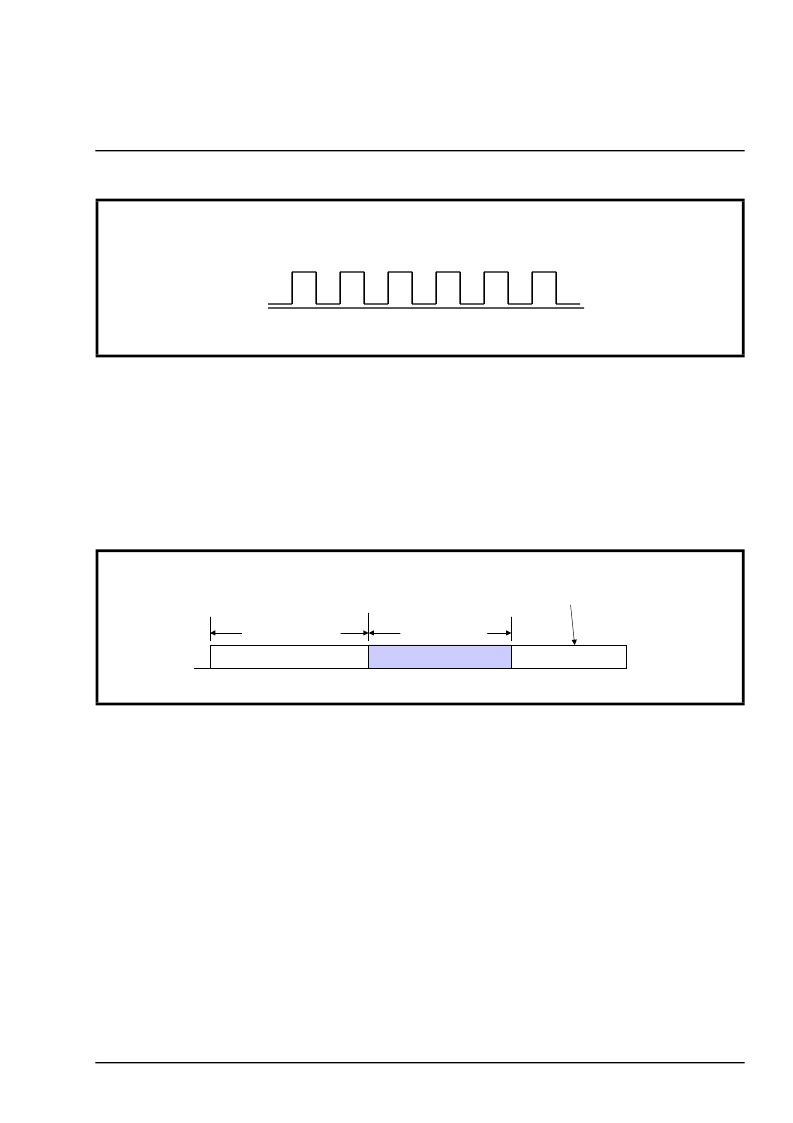

MAJOR PATTERN B is created (by the Mapper IC) by:

Repeating MINOR PATTERN P1 (e.g., 7 clock pulses, followed by a gap) 63 times.

Upon completion of the 63rd transmission of MINOR PATTERN P1, MINOR PATTERN P2 is transmitted

repeatedly 36 times.

pon completion of the 35th transmission of MINOR PATTERN P2, MINOR PATTERN P3 is transmitted once.

Figure 62 presents an illustration which depicts the procedure that is used to synthesize MAJOR PATTERN B.

Hence, MAJOR PATTERN B consists of "(63 x 7) + (35 x 5)" + 6 = 622 clock pulses.

These 622 clock pulses were delivered over a period of "(63 x 8) + (35 x 6) + 6 = 720 STS-1 (or 51.84MHz)

clock periods.

PUTTING THE PATTERNS TOGETHER

Finally, the DS3 to OC-N Mapper IC clock output is reproduced by doing the following.

MAJOR PATTERN A is transmitted two times (repeatedly).

After the second transmission of MAJOR PATTERN A, MAJOR PATTERN B is transmitted once.

Then the whole process repeats.

Throughout the remainder of this document, we will refer to this particular pattern as the "SUPER PATTERN".

Figure 63 presents an illustration of this "SUPER PATTERN" which is output via the Mapper IC.

F

IGURE

61. I

LLUSTRATION

OF

MINOR PATTERN P3

F

IGURE

62. I

LLUSTRATION

OF

P

ROCEDURE

WHICH

IS

USED

TO

S

YNTHESIZE

PATTERN B

1 2 3 4 5

6

PATTERN P1

PATTERN P2

Repeats 63 Times

Repeats 35 Times

PATTERN P3

Transmitted 1 Time

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75L04 | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L04IV | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L06D | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L06DIB | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L06 | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75L04DIV-F | 功能描述:外圍驅(qū)動器與原件 - PCI 4-Ch DS3, E3, STS-1 RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75L04DIVTR | 功能描述:時鐘合成器/抖動清除器 4 CHNL E3/DS3/STS 1 JITTER ATTENUATOR RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L04DIVTR-F | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L04ES | 功能描述:時鐘合成器/抖動清除器 4CH T3/E3/STS1 LIU+JA 3.3V RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L04IV | 功能描述:外圍驅(qū)動器與原件 - PCI 4CH E3/DS3/STS1 JITTER ATTENUATOR RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。