- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R12IB (EXAR CORP) TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR PDF資料下載

參數(shù)資料

| 型號: | XRT75R12IB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PBGA420 |

| 封裝: | 35 X 35 MM, TBGA-420 |

| 文件頁數(shù): | 73/89頁 |

| 文件大?。?/td> | 457K |

| 代理商: | XRT75R12IB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當(dāng)前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

PRELIMINARY

XRT75R12

REV. P1.0.2

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

70

T

ABLE

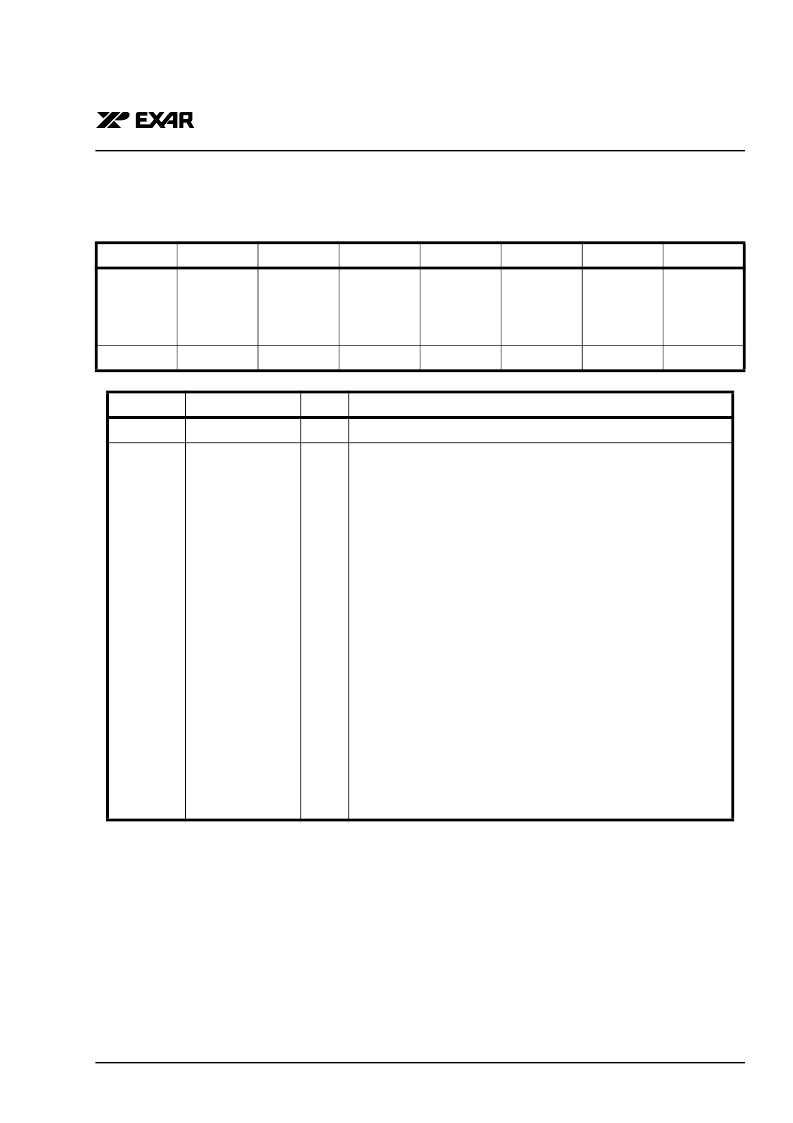

30: XRT75R12 R

EGISTER

MAP

SHOWING

A

LARM

S

TATUS

R

EGISTERS

(AS_

N

)

T

ABLE

31: A

LARM

S

TATUS

R

EGISTER

- C

HANNEL

N

A

DDRESS

L

OCATION

= 0

XM

3

B

IT

7

B

IT

6

B

IT

5

B

IT

4

B

IT

3

B

IT

2

B

IT

1

B

IT

0

Reserved

Loss of PRBS

Pattern Sync

Digital LOS

Defect

Declared

Analog LOS

Defect

Declared

(FIFO Limit)

Alarm

Declared

Receive LOL

Defect

Declared

Receive LOS

Defect

Declared

Transmit

DMO

Condition

R/O

R/O

R/O

R/O

R/O

R/O

R/O

B

IT

N

UMBER

N

AME

T

YPE

D

ESCRIPTION

7

Reserved

6

Loss of PRBS Pat-

tern Lock

R/O

Loss of PRBS Pattern Lock Indicator:

This READ-ONLY bit-field indicates whether or not the PRBS Receiver

(within the Receive Section of Channel n) is declaring PRBS Lock

within the incoming PRBS pattern.

If the PRBS Receiver detects a very large number of bit-errors within

its incoming data-stream, then it will declare the Loss of PRBS Lock

Condition.

Conversely, if the PRBS Receiver were to detect its pre-determined

PRBS pattern with the incoming DS3, E3 or STS-1 data-stream, (with

little or no bit errors) then the PRBS Receiver will clear the Loss of

PRBS Lock condition.

0 - Indicates that the PRBS Receiver is currently declaring the PRBS

Lock condition within the incoming DS3, E3 or STS-1 data-stream.

1 - Indicates that the PRBS Receiver is currently declaring the Loss of

PRBS Lock condition within the incoming DS3, E3 or STs-1 data-

stream.

N

OTE

:

This register bit is only valid if all of the following are true.

a.

The PRBS Generator block (within the Transmit Section of the

Chip is enabled).

b.

The PRBS Receiver is enabled.

c.

The PRBS Pattern (that is generated by the PRBS Generator) is

somehow looped back into the Receive Path (via the Line-Side)

and in-turn routed to the receive input of the PRBS Receiver.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75VL00 | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00IV | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT79L71 | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L71IB | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L72 | 2 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R12IB-F | 功能描述:外圍驅(qū)動器與原件 - PCI 12 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75R12IB-L | 功能描述:LIN 收發(fā)器 Attenuator RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT75VL00 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00D | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。