- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R12IB (EXAR CORP) TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR PDF資料下載

參數(shù)資料

| 型號: | XRT75R12IB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PBGA420 |

| 封裝: | 35 X 35 MM, TBGA-420 |

| 文件頁數(shù): | 81/89頁 |

| 文件大小: | 457K |

| 代理商: | XRT75R12IB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁當(dāng)前第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

PRELIMINARY

XRT75R12

REV. P1.0.2

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR

78

B

IT

N

UMBER

N

AME

T

YPE

D

ESCRIPTION

7 - 6

Reserved

5

PRBS Enable

R/W

PRBS Generator and Receiver Enable - Channel_n:

This READ/WRITE bit-field is used to enable or disable the PRBS

Generator and Receiver within a given Channel of the XRT75R12.

If the user enables the PRBS Generator and Receiver, then the follow-

ing will happen.

1.

The PRBS Generator (which resides within the Transmit Section

of the Channel) will begin to generate an unframed, 2^15-1

PRBS Pattern (for DS3 and STS-1 applications) and an

unframed, 2^23-1 PRBS Pattern (for E3 applications).

2.

The PRBS Receiver (which resides within the Receive Section

of the Channel) will now be enabled and will begin to search the

incoming data for the above-mentioned PRBS patterns.

0 - Disables both the PRBS Generator and PRBS Receiver within the

corresponding channel.

1 - Enables both the PRBS Generator and PRBS Receiver within the

corresponding channel.

N

OTES

:

1.

To check and monitor PRBS Bit Errors, DR (Dual Rail) mode

will be over-ridden and Single Rail mode forced for the

duration of this mode. This will configure the RNEG/LCV_n

output pin to function as a PRBS Error Indicator. All errors

will be flagged on this pin. The errors will also be

accumulated in the 16 bit Error counter for the channel.

2.

If the user enables the PRBS Generator and PRBS Receiver,

the Channel will ignore the data that is being accepted from

the System-side Equipment (via the TxPOS_n and TxNEG_n

input pins) and will overwrite this outbound data with the

PRBS Pattern.

3.

The system must provide an accurate and stable data-rate

clock to the TxClk_n pin during this operation.

4

RLB_n

R/W

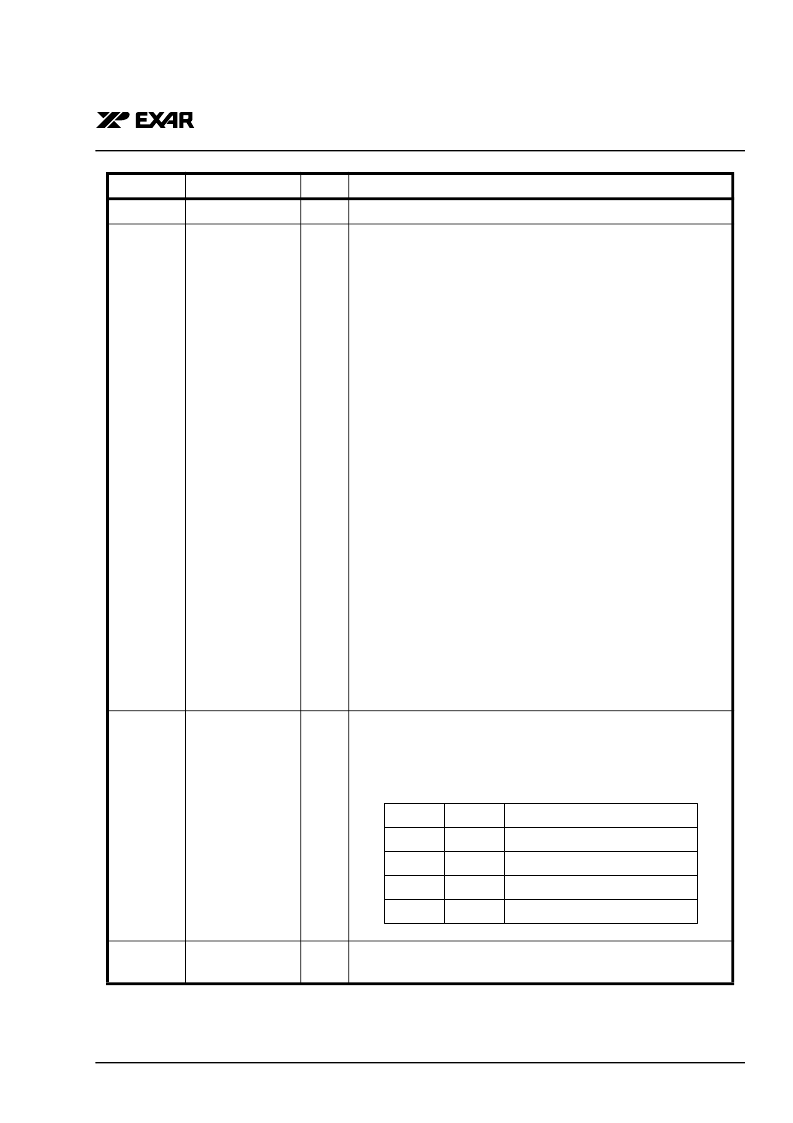

Loop-Back Select - RLB Bit - Channel_n:

This READ/WRITE bit-field along with the corresponding LLB_n bit-

field is used to configure a given channel into various loop-back modes

ass shown by the following table.

3

LLB_n

R/W

Loop-Back Select - LLB Bit-field - Channel_n:

See the table (above) for RLB_n.

Loop-back Mode

Digital Local Loop-back Mode

Analog Local Loop-back Mode

Remote Loop-back Mode

Normal (No Loop-back) Mode

RLB_n

1

0

1

0

LLB_n

1

1

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75VL00 | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00IV | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT79L71 | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L71IB | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| XRT79L72 | 2 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R12IB-F | 功能描述:外圍驅(qū)動器與原件 - PCI 12 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75R12IB-L | 功能描述:LIN 收發(fā)器 Attenuator RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT75VL00 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00_08 | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00D | 制造商:EXAR 制造商全稱:EXAR 功能描述:E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。