- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄9999 > XRT75VL00DIVTR (Exar Corporation)IC LIU E3/DS3/STS-1 1CH 52TQFP PDF資料下載

參數(shù)資料

| 型號: | XRT75VL00DIVTR |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 60/92頁 |

| 文件大小: | 0K |

| 描述: | IC LIU E3/DS3/STS-1 1CH 52TQFP |

| 標準包裝: | 1,000 |

| 類型: | 線路接口裝置(LIU) |

| 驅(qū)動器/接收器數(shù): | 1/1 |

| 規(guī)程: | DS3,E3,STS-1 |

| 電源電壓: | 3.135 V ~ 3.465 V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 52-LQFP |

| 供應商設備封裝: | 52-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

XRT75VL00D

58

REV. 1.0.4

E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

As a consequence, no "Mapping/De-Mapping" Jitter or Wander is induced in the "Ideal Case".

9.2.2.2

The 44.736Mbps + 1ppm Case

The "above example" was a very ideal case. In reality, there are going to be frequency offsets in both the DS3

and STS-1 signals. For instance Bellcore GR-499-CORE mandates that a DS3 signal have a bit rate of

44.736Mbps ± 20ppm. Hence, the bit-rate of a "Bellcore" compliant DS3 signal can vary from the exact correct

frequency for DS3 by as much of 20ppm in either direction. Similarly, many SONET applications mandate that

SONET equipment use at least a "Stratum 3" level clock as its timing source. This requirement mandates that

an STS-1 signal must have a bit rate that is in the range of 51.84 ± 4.6ppm. To make matters worse, there are

also provisions for SONET equipment to use (what is referred to as) a "SONET Minimum Clock" (SMC) as its

timing source. In this case, an STS-1 signal can have a bit-rate in the range of 51.84Mbps ± 20ppm.

In order to convey the impact that frequency offsets (in either the DS3 or STS-1 signal) will impose on the bit-

stuffing behavior, and the resulting bit-rate, intrinsic jitter and wander within the DS3 signal that is being

transported across the SONET network; let us assume that a DS3 signal, with a bit-rate of 44.736Mbps +

1ppm is being mapped into an STS-1 signal with a bit-rate of 51.84Mbps + 0ppm. In this case, the following

things will occur.

In general, most of the STS-1 SPE's will each transport 5592 DS3 data bits.

However, within a "one-second" period, a DS3 signal that has a bit-rate of 44.736Mbps + 1 ppm will deliver

approximately 44.7 additional bits (over and above that of a DS3 signal with a bit-rate of 44.736Mbps + 0

ppm). This means that this particular signal will need to "negative-stuff" or map in an additional DS3 data bit

every (1/44.736 =) 22.35ms. In other words, this additional DS3 data bit will need to be mapped into about

one in every (22.35ms 8000 =) 178.8 STS-1 SPEs in order to avoid dropping any DS3 data-bits.

What does this mean at the "Source" PTE?

All of this means that as the "Source" PTE maps this DS3 signal, with a data rate of 44.736Mbps + 1ppm into

an STS-1 signal, most of the resulting "outbound" STS-1 SPEs will transport 5592 DS3 data bits (e.g., 3 Stuff

Opportunity bits will be carrying DS3 data bits, the remaining 6 Stuff Opportunity bits are "stuff" bits, as in the

"Ideal" case). However, in approximately one out of 178.8 "outbound" STS-1 SPEs, there will be a need to

insert an additional DS3 data bit within this STS-1 SPE. Whenever this occurs, then (for these particular STS-

1 SPEs) the SPE will be carrying 5593 DS3 data bits (e.g., 4 Stuff Opportunity bits will be carrying DS3 data

bits, the remaining 5 Stuff Opportunity bits are "stuff" bits).

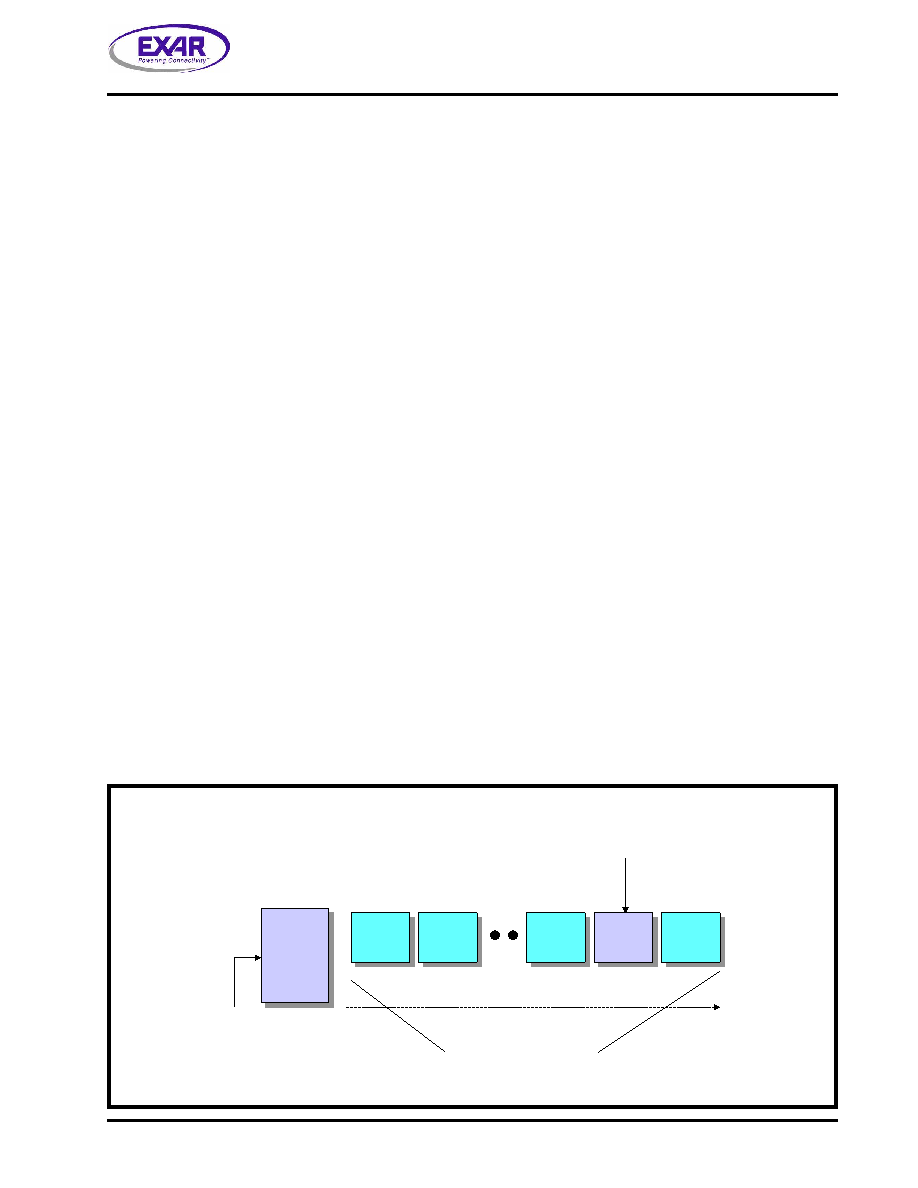

Figure 39 presents an illustration of the STS-1 SPE traffic that will be generated by the "Source" PTE, during

this condition.

FIGURE 39. AN ILLUSTRATION OF THE STS-1 SPE TRAFFIC THAT WILL BE GENERATED BY THE "SOURCE" PTE,

WHEN MAPPING IN A

DS3 SIGNAL THAT HAS A BIT RATE OF 44.736MBPS + 1PPM, INTO AN STS-1 SIGNAL

Source

PTE

Source

PTE

44.736Mbps + 1ppm

5592

DS3 Data

Bits

5592

DS3 Data

Bits

5592

DS3 Data

Bits

5592

DS3 Data

Bits

SPE # N

SPE # N+1

5592

DS3 Data

Bits

5592

DS3 Data

Bits

SPE # N+177

5593

DS3 Data

Bits

5593

DS3 Data

Bits

5592

DS3 Data

Bits

5592

DS3 Data

Bits

SPE # N+178

SPE # N+179

Extra DS3 Data

Bit Stuffed Here

STS-1 SPE Data Stream

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MS27468T9B35S EDR | CONN RCPT 6POS JAM NUT W/SCKT |

| MS27466T23B35SD | CONN RCPT 100POS WALL MNT W/SCKT |

| MS27466E15A35P | CONN RCPT 37POS WALL MNT W/PINS |

| VI-B40-IV-F1 | CONVERTER MOD DC/DC 5V 150W |

| MS27497T10B5PA | CONN RCPT 5POS WALL MNT W/PINS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75VL00DIVTR-F | 功能描述:時鐘合成器/抖動清除器 3.3V 1 CH E3/DS3/STS W/SONET DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75VL00ES | 功能描述:時鐘合成器/抖動清除器 1CHT3/E3/STS1LIU+A 3.3V VOLTAGE DRIVE RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75VL00IV | 功能描述:外圍驅(qū)動器與原件 - PCI 3.3V 1 CH E3/DS3/STS W/JITTER ATTEN RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75VL00IV-F | 功能描述:外圍驅(qū)動器與原件 - PCI 3.3V 1 CH E3/DS3/STS W/JITTER ATTEN RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75VL00IVTR | 功能描述:時鐘合成器/抖動清除器 3.3V 1 CH E3/DS3/STS W/JITTER ATTEN RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。