- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄2121 > XRT91L32IQTR (Exar Corporation)IC TXRX SONET/SDH 8BIT 100QFP PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L32IQTR |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 2/37頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC TXRX SONET/SDH 8BIT 100QFP |

| 產(chǎn)品變化通告: | XRT91L32IQ(TR) Obsolescence 12/Oct/2010 |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | SONET/SDH |

| 電源電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-BQFP |

| 供應(yīng)商設(shè)備封裝: | 100-QFP(14x20) |

| 包裝: | 帶卷 (TR) |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)

XRT91L32

xr

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

REV. 1.0.3

8

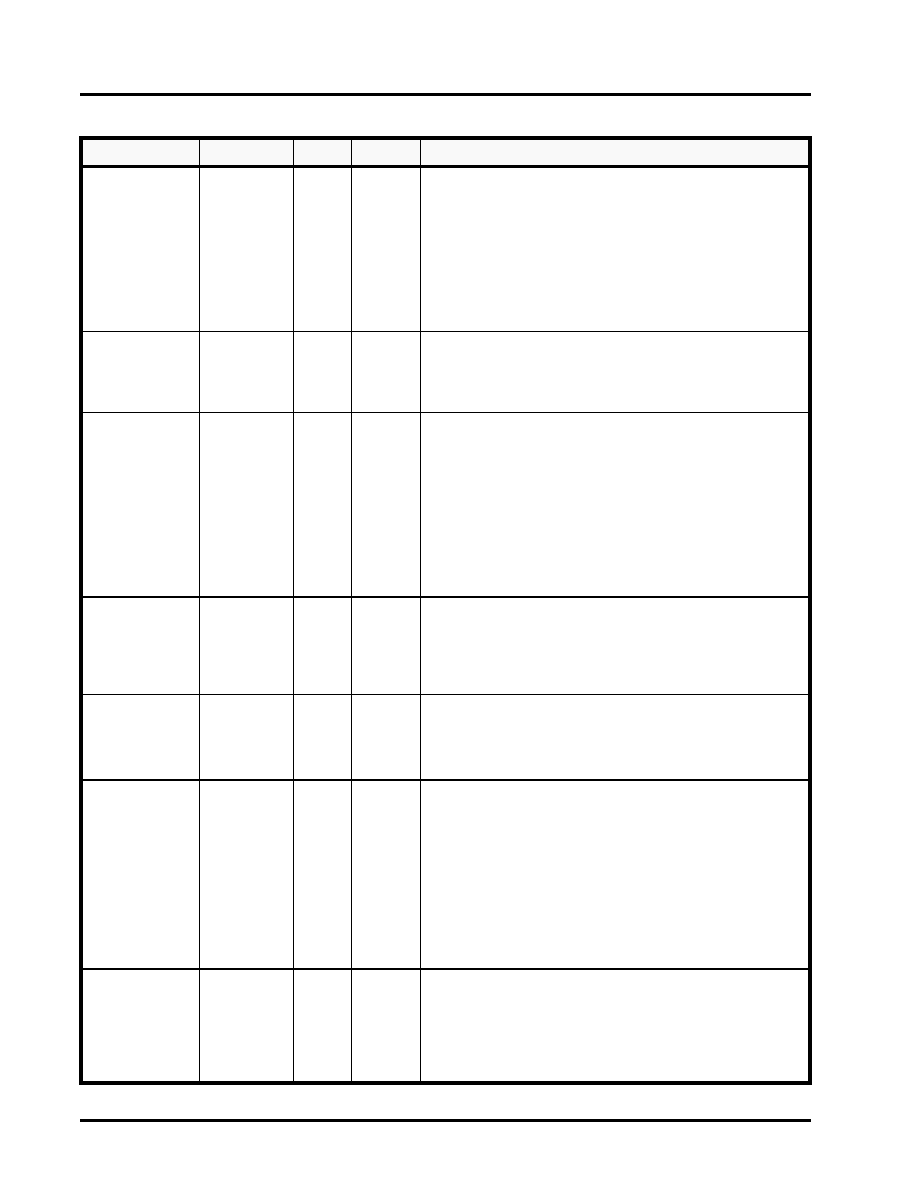

RECEIVER SECTION

NAME

LEVEL

TYPE

PIN

DESCRIPTION

RXDO0

RXDO1

RXDO2

RXDO3

RXDO4

RXDO5

RXDO6

RXDO7

LVTTL

O

35

36

38

39

41

42

44

45

Receive Parallel Data Output

77.76 Mbps (STS-12/STM-4) / 19.44 Mbps (STS-3/STM-1)

8-bit parallel receive data output is updated simultaneously on

the rising edge of the RXPCLKO output. The 8-bit parallel inter-

face is de-multiplexed from the receive serial data input MSB

first (RXDO[7:0]). The XRT91L32 will output the data on the

rising edge of this clock.

RXIP

RXIN

Diff LVPECL

I

24

25

Receive Serial Data Input

The differential receive serial data stream of 622.08 Mbps

STS-12/STM-1 or 155.52 Mbps STS-3/STM-1 is applied to

these input pins.

XRXCLKIP

XRXCLKIN

Diff LVPECL

I

19

20

External Recovered Receive Clock Input

The differential receive serial data stream of 622.08 Mbps

STS-12/STM-1 or 155.52 Mbps STS-3/STM-1 is sampled on

the rising edge of this externally recovered differential clock

coming from the optical module. It is used when the internal

CDR unit is disabled and bypassed by the CDRDIS pin.

NOTE: In the event that XRXCLKIP/N differential input pins are

unused, XRXCLKIP should be tied to VCC with a 1k

Ohm pull-up and XRXCLKIN should be tied to Ground

with a 1k Ohm pull-down.

RXPCLKO

LVTTL

O

47

Receive Parallel Clock Output (77.76 MHz or 19.44 MHz)

77.76 MHz (STS-12/STM-4) or 19.44 MHz (STS-3/STM-1)

clock output reference for the 8-bit parallel receive data output

RXDO[7:0]. The parallel received data output bus will be

updated on the falling edge of this clock.

CDRAUX-

REFCLK

LVTTL

I

51

Clock and Data Recovery Auxillary Reference Clock

77.76 MHz ± 500 ppm auxillary reference clock for the CDR.

NOTE: In the event that CDRAUXREFCLK LVTTL input pin is

unused, CDRAUXREFCLK should be tied to ground.

OOF

LVTTL

I

22

Out of Frame Input Indicator

This level sensitive input pin is used to initiate frame detection

and byte alignment recovery when OOF is declared by the

downstream device. When this pin is held High, FRAME-

PULSE will pulse for a single RXPCLKO period upon the detec-

tion of every third frame alignment A2 byte in the incoming

SONET/SDH Frame.

"Low" = Normal Operation

"High" = OOF Indication initiating frame detection and byte

boundary recovery and activating FRAMEPULSE

FRAMEPULSE

LVTTL

O

48

Sonet Frame Alignment Pulse

This pin will generate a single pulse for an RXPCLKO clock

period upon the detection of the third frame alignment A2 byte

whenever the OOF input pin is held High. The parallel received

data output bus will then be byte aligned to this newly recov-

ered SONET/SDH frame.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L80IB-F | IC TXRX SONET/SDH 4BIT 196STBGA |

| ZSD100N8TA | IC DRIVER SIREN 8-SOIC |

| ZXCD1210JB16TA | IC AMP AUDIO CLASS D 16QFN |

| ZXFV203N14TC | IC AMP VIDEO CFA 3CHAN 14SOIC |

| 020189 | FAN 115VAC 254X89MM CLE2T2 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L32IQTR-F | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L33 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

| XRT91L33AIG-F | 制造商:Exar Corporation 功能描述:CDR 155.52Mbps/622.08Mbps SONET/SDH 20-Pin TSSOP |

| XRT91L33ES | 功能描述:界面開(kāi)發(fā)工具 Eval System for XRT91L33 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評(píng)估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XRT91L33IG | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。