- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄2121 > XRT91L32IQTR (Exar Corporation)IC TXRX SONET/SDH 8BIT 100QFP PDF資料下載

參數(shù)資料

| 型號(hào): | XRT91L32IQTR |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 6/37頁 |

| 文件大小: | 0K |

| 描述: | IC TXRX SONET/SDH 8BIT 100QFP |

| 產(chǎn)品變化通告: | XRT91L32IQ(TR) Obsolescence 12/Oct/2010 |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 類型: | 收發(fā)器 |

| 規(guī)程: | SONET/SDH |

| 電源電壓: | 3.3V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-BQFP |

| 供應(yīng)商設(shè)備封裝: | 100-QFP(14x20) |

| 包裝: | 帶卷 (TR) |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

XRT91L32

xr

STS-12/STM-4 OR STS-3/STM-1 SONET/SDH TRANSCEIVER

REV. 1.0.2

12

2.0

RECEIVE SECTION

The receive section of XRT91L32 include the inputs RXIP/N, followed by the clock and data recovery unit

(CDR) and receive serial-to-parallel converter. The receiver accepts the high speed Non-Return to Zero (NRZ)

serial data at 622.08 Mbps or 155.52 Mbps through the input interfaces RXIP/N. The clock and data recovery

unit recovers the high-speed receive clock from the incoming scrambled NRZ data stream. The recovered

serial data is converted into an 8-bit-wide, 77.76 Mbps or 19.44 Mbps parallel data and presented to the

RXDO[7:0] parallel interface. This parallel interface is designed for Single-Ended LVTTL operation. A divide-

by-8 version of the high-speed recovered clock RXPCLKOP/N, is used to synchronize the transfer of the 8-bit

RXDO[7:0] data with the receive portion of the framer/mapper device. Upon initialization or loss of signal or

loss of lock, the external reference clock signal of 19.44 MHz or 77.76 MHz is used to start-up the clock

recovery phase-locked loop for proper operation. In certain applications, the CDR block on the XRT91L32 can

be disabled and bypassed by enabling the CDRDIS pin to permit the flexibility of using an externally recovered

receive clock thru the XRXCLKIP/N pins.7

2.1

Receive Serial Input

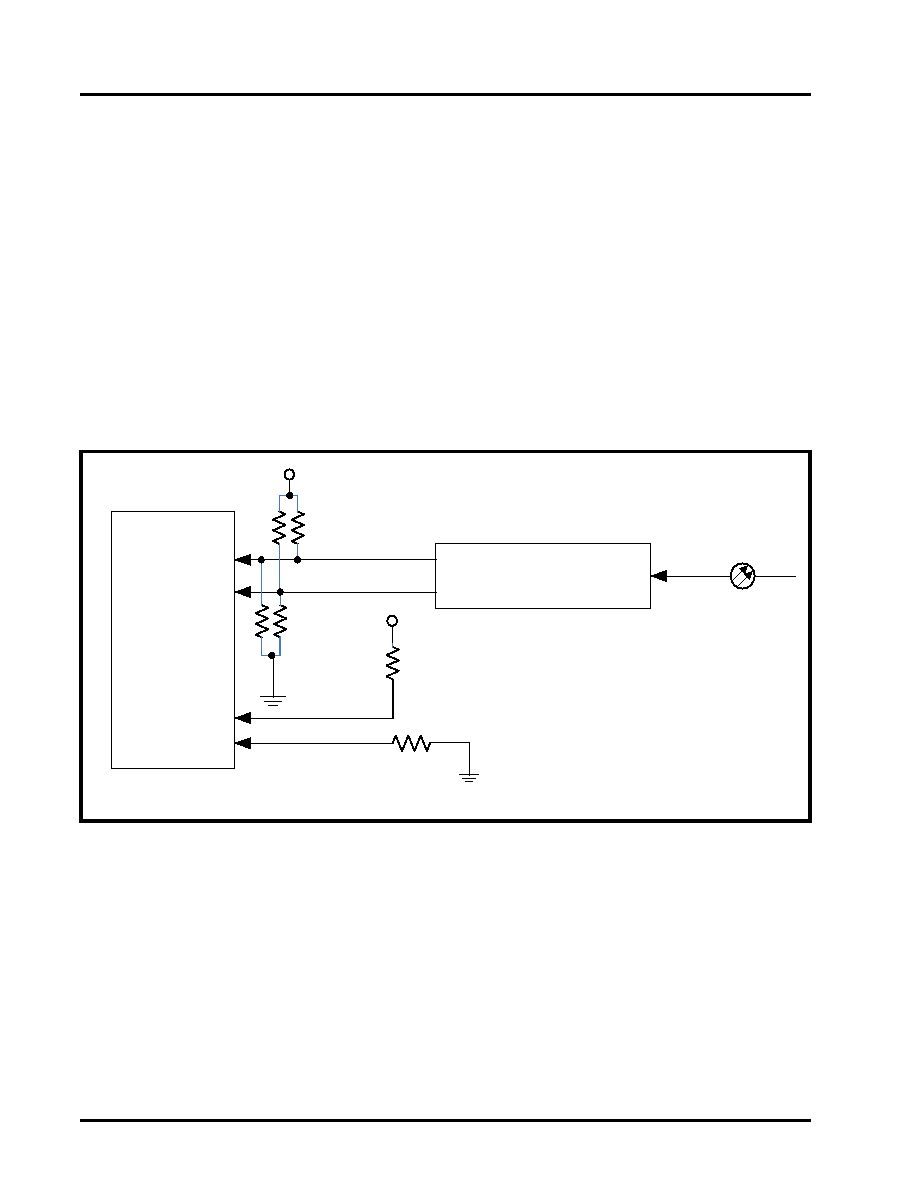

The receive serial inputs are applied to RXIP/N. The receive serial inputs can be AC or DC coupled to an

optical module or an electrical interface. A simplified AC coupling block diagram is shown in Figure 3.(Also,

refer to application note TAN-9132.)

NOTE: Some optical modules integrate AC coupling capacitors within the module. AC or DC coupling is largely specific to

system design and optical module of choice.

FIGURE 3. RECEIVE SERIAL INPUT INTERFACE BLOCK

SFP, Optical Module

RXIP

RXIN

Optical Fiber

XRT91L32

STS-12/STM-4

or

STS-3/STM-1

Transceiver

82 Ohm

130 Ohm

XRXCLKIP

XRXCLKIN

(optional)

1KOhm

Install terminators close to

RXIP and RXIN pins

Tie unused differential input pins

to VCC and GND

Internally

AC coupled

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L80IB-F | IC TXRX SONET/SDH 4BIT 196STBGA |

| ZSD100N8TA | IC DRIVER SIREN 8-SOIC |

| ZXCD1210JB16TA | IC AMP AUDIO CLASS D 16QFN |

| ZXFV203N14TC | IC AMP VIDEO CFA 3CHAN 14SOIC |

| 020189 | FAN 115VAC 254X89MM CLE2T2 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L32IQTR-F | 功能描述:LIN 收發(fā)器 PHY Transceiver RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT91L33 | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

| XRT91L33AIG-F | 制造商:Exar Corporation 功能描述:CDR 155.52Mbps/622.08Mbps SONET/SDH 20-Pin TSSOP |

| XRT91L33ES | 功能描述:界面開發(fā)工具 Eval System for XRT91L33 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XRT91L33IG | 制造商:EXAR 制造商全稱:EXAR 功能描述:STS-12/STS-3 MULTIRATE CLOCK AND DATA RECOVERY UNIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。