- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372956 > XWM8711EDS (Wolfson Microelectronics) Internet Audio DAC with Integrated Headphone Driver PDF資料下載

參數(shù)資料

| 型號(hào): | XWM8711EDS |

| 廠商: | Wolfson Microelectronics |

| 英文描述: | Internet Audio DAC with Integrated Headphone Driver |

| 中文描述: | 互聯(lián)網(wǎng)音頻DAC集成耳機(jī)驅(qū)動(dòng)器 |

| 文件頁(yè)數(shù): | 17/36頁(yè) |

| 文件大?。?/td> | 379K |

| 代理商: | XWM8711EDS |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

WM8711

Product Preview

WOLFSON MICROELECTRONICS LTD

PP Rev 1.2 November 2000

17

CLKOUT can also be divided by 2 under software control, refer to Table 7. Note that if CLKOUT is

not required then the CLKOUT buffer on the WM8711 can be safely powered down to conserve

power (see POWER DOWN section). If the system architect has the choice between using F

CLKOUT

=

F

MCLK

or F

CLKOUT

= F

MCLK

/2 in the interface, the latter is recommended to conserve power. When the

divide by two is selected CLKOUT changes on the rising edge of MCLK. Please refer to Electrical

Characteristics for timing information.

REGISTER

ADDRESS

0001000

Sampling

Control

BIT

LABEL

DEFAULT

DESCRIPTION

7

CLKODIV2

0

CLKOUT divider select

1 = CLOCKOUT is Core Clock

divides by 2

0 = CLOCKOUT is Core Clock

Table 7 Programming CLKOUT

CLKOUT is disabled and set low whenever the device is in reset.

DIGITAL AUDIO INTERFACES

WM8711 may be operated in either one of the 4 offered audio interface modes. These are:

Right justified

Left justified

I2S

DSP mode

All four of these modes are MSB first and operate with data 16 to 32 bits, except in right justified

mode where 32 bit data is not supported.

The digital audio interface receives the digital audio data for the internal DAC digital filters on the

DACDAT input. DACDAT is the formatted digital audio data stream output to the DAC digital filters

with left and right channels multiplexed together. DACLRC is an alignment clock that controls

whether Left or Right channel data is present on DATDAT. DACDAT and DACLRC are synchronous

with the BCLK signal with each data bit transition signified by a BCLK transition. DACDAT is always

an input. BCLK and DACLRC are either outputs or inputs depending whether the device is in master

or slave mode. Refer to the MASTER/SLAVE OPERATION section

There are four digital audio interface formats accommodated by the WM8711. These are shown in

the figures below. Refer to the Electrical Characteristic section for timing information.

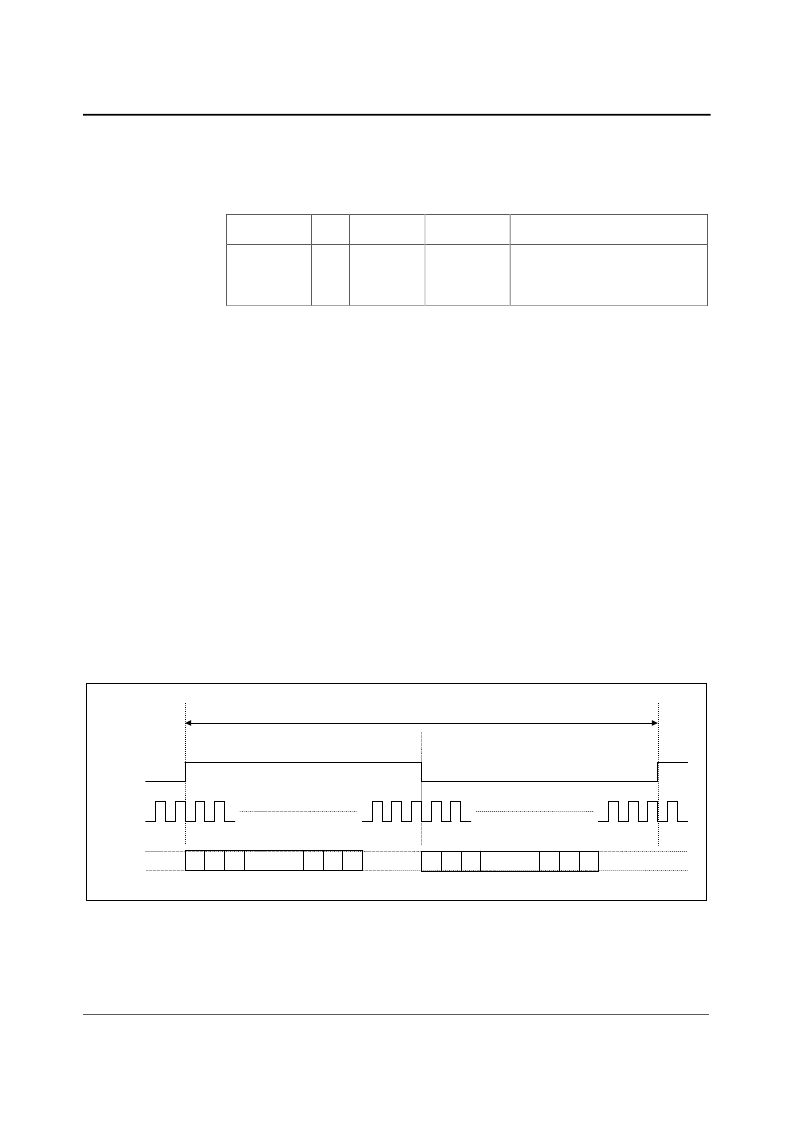

Left Justified mode is where the MSB is available on the first rising edge of BCLK following a

DACLRC transition.

LEFT CHANNEL

RIGHT CHANNEL

DACLRC

BCLK

DACDAT

1/fs

n

3

2

1

n-2

n-1

LSB

MSB

n

3

2

1

n-2

n-1

LSB

MSB

Figure 13 Left Justified Mode

I2S mode is where the MSB is available on the 2nd rising edge of BCLK following a LRCLK

transition.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XWM8721EDS | Internet Audio DAC with Integrated Headphone Driver |

| XWM8722EDS | Stereo DAC with Integrated Tone Generator and Line/Variable Level Outputs |

| XWM8728EDS | 24-bit, 192kHz Stereo DAC with Volume Control and DSD Support |

| XWM8729ED | 24-bit, 192kHz Stereo DAC |

| XWM8731EDS | Portable Internet Audion CODEC with Headphone Driver and Programmable Sample Rates |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XWM8721EDS | 制造商:WOLFSON 制造商全稱:WOLFSON 功能描述:Internet Audio DAC with Integrated Headphone Driver |

| XWM8721EDS/R | 制造商:WOLFSON 制造商全稱:WOLFSON 功能描述:Internet Audio DAC with Integrated Headphone Driver |

| XWM8722EDS | 制造商:WOLFSON 制造商全稱:WOLFSON 功能描述:Stereo DAC with Integrated Tone Generator and Line/Variable Level Outputs |

| XWM8728EDS | 制造商:WOLFSON 制造商全稱:WOLFSON 功能描述:24-bit, 192kHz Stereo DAC with Volume Control |

| XWM8728EDS/R | 制造商:WOLFSON 制造商全稱:WOLFSON 功能描述:24-bit, 192kHz Stereo DAC with Volume Control |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。