- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373760 > Z53C80SCSI (ZiLOG, Inc.) SMALL COMPUTER SYSTEM INTERFACE (SCSI) PDF資料下載

參數(shù)資料

| 型號: | Z53C80SCSI |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| 中文描述: | 小型計(jì)算機(jī)系統(tǒng)接口(SCSI) |

| 文件頁數(shù): | 14/40頁 |

| 文件大小: | 447K |

| 代理商: | Z53C80SCSI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

14

Z53C80 SCSI

PS97SCC0200

Z

ILOG

FUNCTIONAL DESCRIPTION

(Continued)

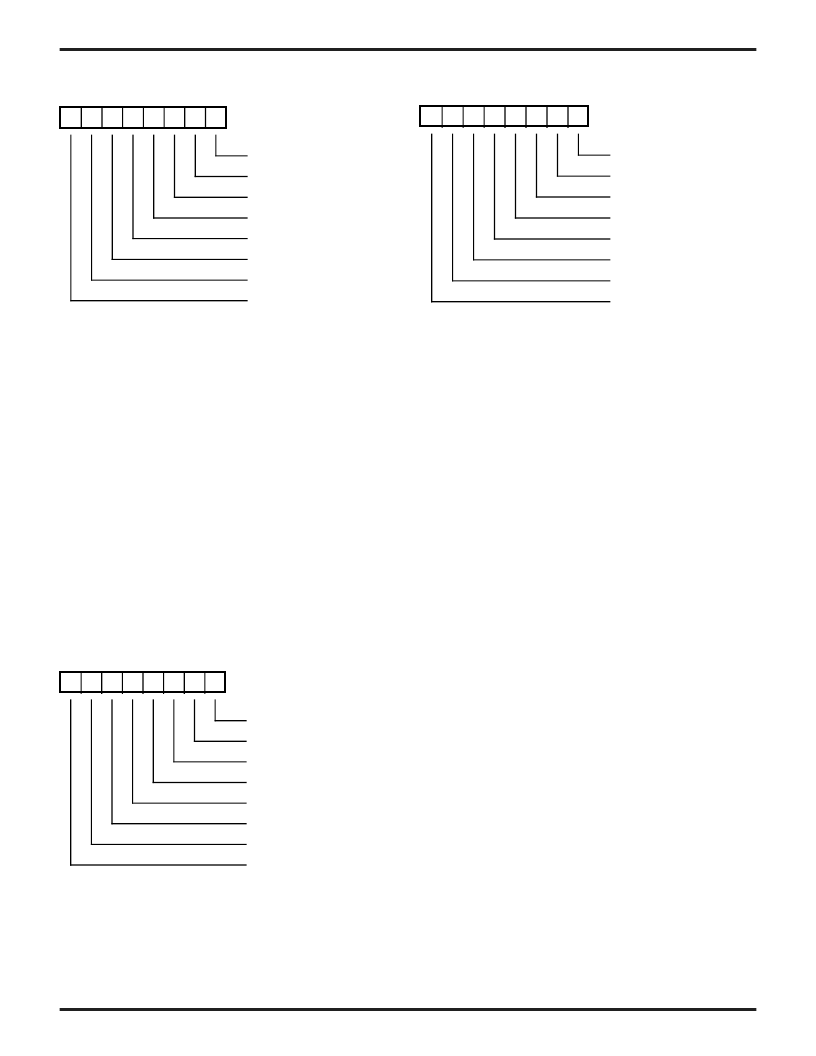

Figure 16. Current SCSI Bus Status Register

End of Process (EOP) Interrupt.

An End Of Process

signal (EOP) which occurs during a DMA transfer (DMA

Mode True) will set the End of DMA Status bit (Bus and

Status Register bit 7) and will optionally generate an

interrupt if Enable EOP Interrupt bit (Mode Register, bit 3)

is True. The /EOP pulse will not be recognized (End of DMA

bit set) unless /EOP, /DACK, and either /RD or /WR are

concurrently active for at least 50 ns. DMA transfers can

still occur if /EOP was not asserted at the correct time. This

interrupt is disabled by resetting the Enable EOP Interrupt

bit.

The proper values for the Bus and Status Register and the

Current SCSI Bus Status Register for this interrupt are

shown in Figures 17 and 18.

Figure 17. Bus and Status Register

Figure 18. Current SCSI Bus Status Register

The End of DMA bit is used to determine when a block

transfer is complete. Receive operations are complete

when there is no data left in the chip and no additional

handshakes occurring. The only exception to this is

receiving data as an Initiator and the Target opts to send

additional data for the same phase. In this /REQ goes

active and the new data is present in the Input Data

Register. Since a phase-mismatch interrupt will not occur,

/REQ and /ACK need to be sampled to determine that the

Target is attempting to send more data.

For send operations, the End of DMA bit is set when the

DMA finishes its transfers, but the SCSI transfer may still be

in progress. If connected as a Target, /REQ and /ACK

should be sampled until both are False. If connected as an

Initiator, a phase change interrupt is used to signal the

completion of the previous phase. It is possible for the

Target to request additional data for the same phase. In

this case, a phase change will not occur and both /REQ

and /ACK are sampled to determine when the last byte was

transferred.

SCSI Bus Reset.

The SCSI generates an interrupt when

the /RST signal transitions to True. The device releases all

bus signals within a bus-clear delay of this transition. This

interrupt also occurs after setting the Assert /RST bit

(Initiator Command Register, bit 7). This interrupt cannot

be disabled. (Note: /RST is not latched in bit 7 of the

Current SCSI Bus Status Register and is not active when

this port is read. For this case, the Bus Reset interrupt is

determined by default.)

The proper values for the Bus and Status Register and the

Current SCSI Bus Status Register are displayed in Figures

19 and 20, respectively.

D7

D0

/DBP

/SEL

I//O

C//D

/MSG

/REQ

/BSY

/RST

0

0

0

X

X

X

0

X

D7

D0

/ACK

/ATN

Busy Error

Phase Match

Interrupt Request Active

Parity Error

DMA Request

End of DMA

1

0

0

1

0

0

0

X

D7

D0

/DBP

/SEL

I//O

C//D

/MSQ

/REQ

/BSY

/RST

0

1

1

X

X

X

0

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z54122 | RETRIGGERABLE MONOSTABLE MULTIVIBRATOR |

| Z5U0603 | ceramic chip capacitors |

| Z5U0805 | ceramic chip capacitors |

| Z5U1206 | ceramic chip capacitors |

| Z5U1210 | ceramic chip capacitors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z53E11 | 制造商:OMRON INDUSTRIAL AUTOMATION 功能描述:E5M Operation Manual DX CODE ZA |

| Z53RD431 | 制造商:HVCA & CKE 功能描述:Varistor, MO, 430V, 50000A, 7000pF |

| Z540 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel Atom Processor |

| Z540-TRACEABLE-W/DATA | 功能描述:手持示波器 NIST-CAL-CERT TRACEABLE W/DATA RoHS:否 制造商:Fluke 帶寬:200 MHz 采樣比:2.5 GS/s 顯示器類型:153 mm Full Color LCD 設(shè)備類型:Oscilloscopes |

| Z54122 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RETRIGGERABLE MONOSTABLE MULTIVIBRATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。